中频解调电路中的I2C总线接口电路

[09-12 16:04:47] 来源:http://www.88dzw.com 单片机学习 阅读:8323次

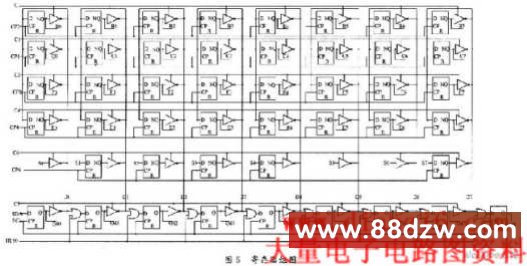

文章摘要:(3)数据串并与并串的转换。电路中,串行数据转换为并行数据、并行数据转换为串行数据主要由移位寄存器完成。它以并行方式与输出模式寄存器和读状态寄存器相连;以串行方式与数据线SDA相连。发送的数据由读状态寄存器装载到数据寄存器中。发送后数据又从串行通道返回数据寄存器中,接收数据时,数据寄存器装入SDA线上的数据。(4)内部总线状态的检测。读状态寄存器连接着内部总线的8位状态位S0~S7,在读状态时,该寄存器将内部总线的状态读进去,再以并行方式传给移位寄存器,移位寄存器以串行的方式传给数据线,即内部总线状态被主控器读取,如图5所示。(5)并行端口的扩展。根据芯片功能的需要,设置了4组输出模式寄存器,

中频解调电路中的I2C总线接口电路,标签:单片机开发,单片机原理,单片机教程,http://www.88dzw.com(3)数据串并与并串的转换。电路中,串行数据转换为并行数据、并行数据转换为串行数据主要由移位寄存器完成。它以并行方式与输出模式寄存器和读状态寄存器相连;以串行方式与数据线SDA相连。发送的数据由读状态寄存器装载到数据寄存器中。发送后数据又从串行通道返回数据寄存器中,接收数据时,数据寄存器装入SDA线上的数据。

(4)内部总线状态的检测。读状态寄存器连接着内部总线的8位状态位S0~S7,在读状态时,该寄存器将内部总线的状态读进去,再以并行方式传给移位寄存器,移位寄存器以串行的方式传给数据线,即内部总线状态被主控器读取,如图5所示。

(5)并行端口的扩展。根据芯片功能的需要,设置了4组输出模式寄存器,分别为调整模式寄存器、备用寄存器、开关模式寄存器、数据模式寄存器。寄存器个数可根据芯片功能的需要进行并行扩展,由于每一组寄存器都对应着相应的子地址,所以每一组寄存器对应相应的时钟CPl,CP2,CP3,CP4和控制端C1,C2,C3,C4。这些时钟和控制端由1个带控制端的2/4译码器输出,所以每次只有1组寄存器工作,如图5所示。

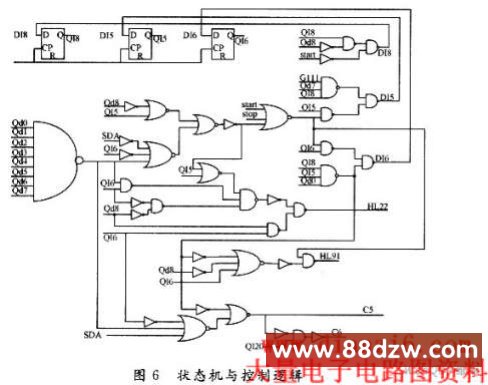

(6)状态机与控制逻辑的设置与优化。状态机与控制逻辑作为I2C接口的控制中心,主要用于控制I2C接口电路的使能、启动、终止。图5给出寄存器组图的应答、复位、选址及中断请求等。通过对状态机与控制逻辑的优化设置,仅使用3位状态作为状态机的状态端,在满足更多功能的基础上,电路更易于实现。如图6所示,3个触发器的输出Q18,Q15,Q16为状态机的状态,Qd0~Qd8为移位寄存器的输出,HL91为移位寄存器的可控复位端,G111为地址检测位,HL22为应答位,C5,C6为移位寄存器与读状态寄存器的控制端。

上电后,状态机的初始值被置位为全0。HL91作为移位寄存器输入端的置位端将移位寄存器的输入端置0。当初始信号到来时,start信号变为1,此时状态机的状态变为100,开始传送寻址字节;当8位地址传送完毕后,假设为写状态,此时Qd8变为高电平,应答位HL22由高电平变为低点平,状态机的状态变为110。HL91变高将移位寄存器的输入置0,响应结束后,应答位由低电平变为高电平,状态机的状态变为010,此时开始传输数据。

I2C总线开始工作后,主控器便发送寻址字节给移位寄存器,在移位寄存器将7位串行地址并行移出,且与地址寄存器的从地址进行比较,当地址相同时,Glll变为1,寻址成功,此时应答信号HL22变为0,并告知主控制器。在寻址成功后,如果为读状态,则在传完该字节之后,产生应答信号,状态机变为100,移位寄存器控制端C5变为低电平,读状态寄存器的控制端C6变为高电平,读状态寄存器读入内部总线状态。其中,QI20是与读/写有关的控制端,响应结束后,状态机状态变为110,此时,C5变为高电平,C6变为低电平,读状态寄存器将存储的8位状态位并行传给移位寄存器;移位寄存器将状态串行移出,发送给主控制器;主控制器接收到8位状态位后,发送非应答信号给接收器,使它释放数据线;响应结束后,主控制器产生结束信号,结束数据传送。

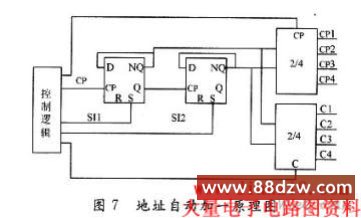

如果为写状态,在接收器产生应答信号后,主控器将发送子地址给移位寄存器。根据输出模式寄存器功能的不同,分别对应3组不同的子地址。在状态机与控制逻辑的作用下,子地址具有自动加1功能,所以在读写多字节时,可以实现自动操作,加上后面的2/4译码器,每次只选通1路输出模式寄存器,如图7所示。

《中频解调电路中的I2C总线接口电路》相关文章

- › 中频解调电路中的I2C总线接口电路

- 在百度中搜索相关文章:中频解调电路中的I2C总线接口电路

- 在谷歌中搜索相关文章:中频解调电路中的I2C总线接口电路

- 在soso中搜索相关文章:中频解调电路中的I2C总线接口电路

- 在搜狗中搜索相关文章:中频解调电路中的I2C总线接口电路

当前位置:

当前位置: