基于单片机控制的带锁相环三路智能同步采集卡设计

[09-12 18:16:42] 来源:http://www.88dzw.com 单片机学习 阅读:8612次

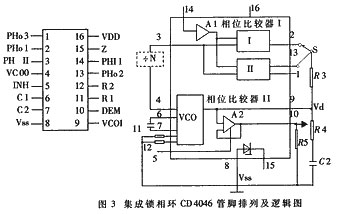

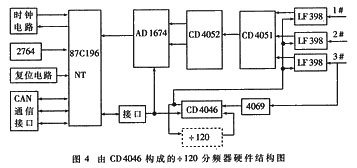

文章摘要:从图3可知:VCO的输出可以经由一除法器进行N分频后,再送至相位比较器Ⅰ,并进而与VI进行相位比较,最后使f2′=f1,二者的相位差恒定,从而实现锁相。由于f2′=f2/N=f1,可推得:f2=Nf1,由此表明:尽管从局部看使用除法器完成的是分频,但就锁相环整体而言却是实现N倍频。本文作者正是利用CD4046的这一特性并配以三片可编程计数器芯片MC14522构成120倍频器(见图4),从而实现三路信号在一个周波内完成120点同步采集。2 系统设计2.1 硬件设计结合上述图1所示的系统硬件结构组成框图及测试性能要求,本系统选用当前较为流行的集成度较高的嵌入式8位单片机87C196NT作为主控器(

基于单片机控制的带锁相环三路智能同步采集卡设计,标签:单片机开发,单片机原理,单片机教程,http://www.88dzw.com |

|---|

从图3可知:VCO的输出可以经由一除法器进行N分频后,再送至相位比较器Ⅰ,并进而与VI进行相位比较,最后使f2′=f1,二者的相位差恒定,从而实现锁相。由于f2′=f2/N=f1,可推得:f2=Nf1,由此表明:尽管从局部看使用除法器完成的是分频,但就锁相环整体而言却是实现N倍频。本文作者正是利用CD4046的这一特性并配以三片可编程计数器芯片MC14522 构成120倍频器(见图4),从而实现三路信号在一个周波内完成120点同步采集。

2 系统设计

2.1 硬件设计

结合上述图1所示的系统硬件结构组成框图及测试性能要求,本系统选用当前较为流行的集成度较高的嵌入式8位单片机87C196NT作为主控器(并扩展了一片EPROM-2764),A/D转换器采用性价比较高且内含由三态缓冲器和锁存器的12位AD1674集成芯片通过三片采样/保持器新片LF398以及多路转换开关CD4051和CD4052的有机组合实现三路信号的同步采集以及AD1674分时转换和量程的自动改变120倍频器由CD4046集成锁相环芯片和整型放大器4069及三片可编程计数器MC14522组成;另外在通讯接口的设计上选用了当前较为流行的CAN串行通信接口。其硬件接线结构图见图4。

|

|---|

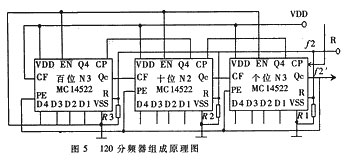

2.2 120分频器设计

根据系统要求(在一个周期内完成三路共120点采集),本系统选用了锁相环芯片CD4046和三片可编程计数器芯片(MC14522),其中三片MC14522按图5所示接线图连接。图中个位所示计数器芯片的输入端(CP端)接从第三路取样后经4069放大器放大、滤波、整形后的输出信号而其输出接4046的PHI1端。总的分频系数N=100N1+10N2+N3,因此,只需给三片计数器置以相应的计数值便可实现相应的分频系数。本系统要求N=120,根据接线图可以分别向百位/十位/个位置计数值1、2、0(即通过单片机向其数据输入端送二进制0001、0010、0000)便可实现120倍的分频,而对于整个锁相环来说则实现了120倍频。

2.3 软件设计

系统软件部分主要是系统主程序、采集子程序、通讯子程序和数字滤波子程序等设计,其中采集子程序作为中断子程序存在;数字滤波采用递推中值算法;所有程序采用C语言编写。

|

|---|

数据采集技术作为一门基础性和综合性相结合的技术,在当今迅速发展的信息时代里起着“基础性和导向”作用,而随着信息技术、计算机技术、微电子技术、控制技术的快速发展在大力推动数据采集技术发展和大范围应用的同时,也对实现数据采集技术的载体――数据采集子系统提出新的和更高的要求:使其进一步朝着微型化、智能化、柔性化方向发展。为此,结合电力系统参数测试的特点和要求,本文作者在设计“三路快速、高精度同步采集卡”过程中,围绕以提高系统性能的目标从系统结构和采集技术两方面都进行了大胆的探索和尝试。经过测试表明:该“智能采集卡”性能稳定可靠,并具有较好的柔性和智能性,较好地满足了设计指标和测试的要求。

《基于单片机控制的带锁相环三路智能同步采集卡设计》相关文章

- › 基于单片机的直接数字频率合成器的设计

- › 基于单片机P89C61X2的FPGA配置

- › 基于单片机的直流调速系统设计

- › 基于单片机仿真器的设计

- › 基于单片机和DSP的被动声目标探测平台设计

- › 基于单片机的电子导游系统设计

- 在百度中搜索相关文章:基于单片机控制的带锁相环三路智能同步采集卡设计

- 在谷歌中搜索相关文章:基于单片机控制的带锁相环三路智能同步采集卡设计

- 在soso中搜索相关文章:基于单片机控制的带锁相环三路智能同步采集卡设计

- 在搜狗中搜索相关文章:基于单片机控制的带锁相环三路智能同步采集卡设计

当前位置:

当前位置: