低频数字相位(频率)测量的CPLD实现

[09-12 18:25:52] 来源:http://www.88dzw.com EDA/PLD 阅读:8477次

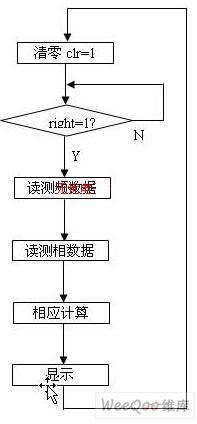

文章摘要:4 结束语由单片机晶振产生的6M信号,经过一个与非门整形为矩形脉冲,再经过CPLD7128的内部设计的分频器分频(分频系数为1000、2000、3000、4000),由该系统进行测频测相。AB二相的信号加上一个反相器,则从理论上讲,相位相差180度。实际测量结果为,频率分别是6000、3000、2000、1500Hz,相位为180度,与理论完全符合。利用DDS数字移相信号发生器产生不同频率和相位差的信号实测证实,该系统指标符合设计要求。随着EDA(电子设计自动化)技术和微电子技术的进步,CPLD的时钟延迟可达到 级,结合其并行工作方式,在超高速、实时测控方面有非常广阔的应用前景;并且CPLD&

低频数字相位(频率)测量的CPLD实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com

4 结束语

由单片机晶振产生的6M信号,经过一个与非门整形为矩形脉冲,再经过CPLD7128的内部设计的分频器分频(分频系数为1000、2000、3000、4000),由该系统进行测频测相。AB二相的信号加上一个反相器,则从理论上讲,相位相差180度。实际测量结果为,频率分别是6000、3000、2000、1500Hz,相位为180度,与理论完全符合。利用DDS数字移相信号发生器产生不同频率和相位差的信号实测证实,该系统指标符合设计要求。

随着EDA(电子设计自动化)技术和微电子技术的进步,CPLD的时钟延迟可达到 级,结合其并行工作方式,在超高速、实时测控方面有非常广阔的应用前景;并且CPLD&FPGA具有高集成度、高可靠性,几乎可将整个设计系统下载于同一芯片中,实现所谓片上系统(SOPC),从而大大缩小其体积,具有可编程型和实现方案容易改动的特点,有利于产品的研制和后期升级。

CPLD7128大约有128个触发器,程序中AB两相计数器共用了19+19=38个,控制部分用了4个,还剩下了大约128-42=86个(其他模块还有少量的占用)。 CPLD7128的计数频率最高可175.4MHz,若提高标频信号的频率为175 MHz,同时增加计数器的长度,则测相精度从理论上讲可以达到0.04度。

采用CPLD配合单片机的设计方案,具有造价较低、速度高、精度高的优点,并且可以通过软件下载而达到仪器硬件升级的目的。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《低频数字相位(频率)测量的CPLD实现》相关文章

- › 低频数字相位(频率)测量的CPLD实现

- › 基于单片机的低频数字相位测量仪的设计

- 在百度中搜索相关文章:低频数字相位(频率)测量的CPLD实现

- 在谷歌中搜索相关文章:低频数字相位(频率)测量的CPLD实现

- 在soso中搜索相关文章:低频数字相位(频率)测量的CPLD实现

- 在搜狗中搜索相关文章:低频数字相位(频率)测量的CPLD实现

分类导航

最新更新

当前位置:

当前位置: