复用器重构降低FPGA成本

[09-12 18:31:49] 来源:http://www.88dzw.com EDA/PLD 阅读:8688次

文章摘要:--- 一般来讲,任何的三个2:1复用器组都可以通过图7或图8的方式转换为一个4:1复用器。但是,这两种转换必须在宽度大于2的复用器总线上进行,以减小所需4-LUT的数量,实际上,如果这两种转换不在总线上进行,将没有意义。--- 总线上2:1复用器三联重新编码是复用器重构算法的核心。 第4节将阐述形成数量最多三联的新方法。4. 复用器总线4.1 “库”的构造--- 压缩减小了其所编码的每一个2:1复用器三联面积,因此,压缩应用在较大的复用器树上最有效。本节阐述大型复用器树是如何构建的。设计中所有的总线都将被存储在一种称为“库”的数据结构中。--- 复用器树采用下面的方法构建。设计中所有2:1复

复用器重构降低FPGA成本,标签:eda技术,eda技术实用教程,http://www.88dzw.com--- 一般来讲,任何的三个2:1复用器组都可以通过图7或图8的方式转换为一个4:1复用器。但是,这两种转换必须在宽度大于2的复用器总线上进行,以减小所需4-LUT的数量,实际上,如果这两种转换不在总线上进行,将没有意义。

--- 总线上2:1复用器三联重新编码是复用器重构算法的核心。 第4节将阐述形成数量最多三联的新方法。

4. 复用器总线

4.1 “库”的构造

--- 压缩减小了其所编码的每一个2:1复用器三联面积,因此,压缩应用在较大的复用器树上最有效。本节阐述大型复用器树是如何构建的。设计中所有的总线都将被存储在一种称为“库”的数据结构中。

--- 复用器树采用下面的方法构建。设计中所有2:1复用器以反向深度顺序排列。这意味着那些离寄存器或者输出引脚最近的复用器将排在列表前面。然后从头至尾扫描列表,寻找每一个2:1复用器,如果其输出仅与另一个2:1复用器相连,则将该复用器和与其相连的复用器一起加到复用器树中。否则,将此2:1复用器作为一个新复用器树的首复用器。以此方式来构建的复用器树含有最大数量的复用器。

--- 如果复用器树中复用器的所有数据输入均不是由同一个树中其他的2:1复用器馈入,则称此复用器为初级输入(对整个树而言)。

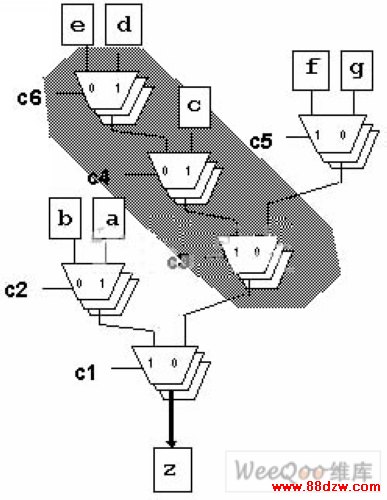

--- 一旦所有的复用器树已经形成,则将其合并成总线。如果两个复用器树要并入同一个总线,它们必须具有相同的结构,即2:1复用器的排列相同,并且都有完全一致的控制输入。这可以通过根据复用器结构,对所有复用器树列表排序来实现,在列表中将结构相同的树靠近排列。总线可直接由结构相同的树构成。

--- 通过规则选取来实现总线宽度最大化。宽总线可以将由压缩引入的控制逻辑开销降低到最小。

--- 4.2 重构

--- 4.3节描述均衡方法,该方法能够使压缩得到的面积减小最大化。均衡建立在重构的基础上,其概念由本节给出。

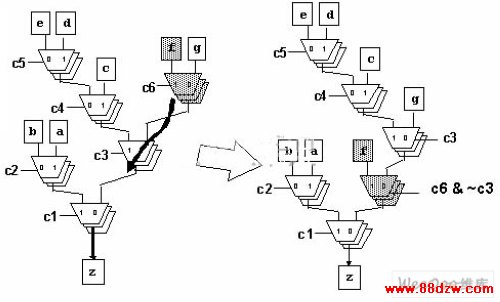

--- 通过2:1复用器所馈入的一个2:1复用器,重构移动该复用器及其一个输入。图9显示了阴影复用器与其“f”输入的重构。为保持原始复用器总线的功能,需要附加一些控制逻辑。这些控制逻辑同样可以由总线上的每一个复用器树来分担。

图9

--- 图9中,重新编码逻辑(c6 AND (NOT c3))必须确保当c1、c3为“假”而c6为“真”时,选择输入“f”(与转换前的情况一致)。同样,当c1、c3、c6为“假”时,选择输入“g”,即(c6 AND (NOT c3))也是“假”。

--- 重构转换将选中的复用器进一步向复用器树顶端移动。因此,不断重复重构转换,可以将任意位置的复用器向顶端移动。

--- 4.3 均衡

--- 压缩通过转换2:1复用器三联,能够减少实现复用器总线所需的4-LUT数量。但是,如果不进行复用器树重构,有些结构是不可能得到最佳三联分组的。例如,无法将图10中所有的2:1复用器进行分组,这是因为每一种可能的分组都将会剩余一个2:1复用器而无法处理。

--- 均衡的目的在于通过最少的重构得到最佳的压缩。对于图10的例子,可以采用图11所示的方法,得到两组2:1复用器三联。

--- 均衡算法由图12的递归定义。由首复用器开始,算法首先均衡复用器树左面和右面数据输入。均衡返回还没有连接为三联的2:1复用器的数量。均衡确保形成尽可能多的三联,这样只会剩余一个或者两个2:1复用器,甚至没有剩余。

--- 均衡中的任何阶段,都需要对1~5个2:1复用器进行均衡(从左侧分支开始最多两个,从右侧分支开始为两个,还要算上当前的2:1复用器本身)。1或2个复用器不会形成更多的三联,而3个复用器总是能够形成三联。4或5个复用器则需要进行重构,以免剩余无法处理的复用器,这种重构方法在图13和图14中示出。

《复用器重构降低FPGA成本》相关文章

- › 复用器重构降低FPGA成本

- 在百度中搜索相关文章:复用器重构降低FPGA成本

- 在谷歌中搜索相关文章:复用器重构降低FPGA成本

- 在soso中搜索相关文章:复用器重构降低FPGA成本

- 在搜狗中搜索相关文章:复用器重构降低FPGA成本

当前位置:

当前位置: