基于FPGA技术的GPS数据加密系统设计研究

[09-12 18:34:43] 来源:http://www.88dzw.com EDA/PLD 阅读:8379次

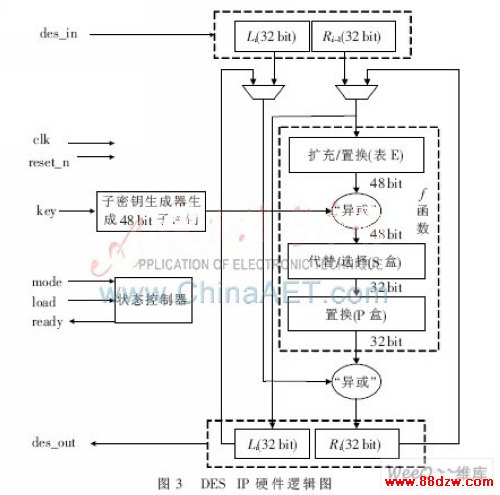

文章摘要:采用软件方式实现的DES算法会在很大程度上占用系统资源,造成系统性能的严重下降,而DES算法本身并没有大量的复杂数学计算(如乘、带进位的加、模等运算),在加密、解密过程和密钥生成过程中仅有逻辑运算和查表运算。因而,无论是从系统性能还是加、解密速度的角度来看,采用硬件实现都是一个理想的方案[3]。图3为DES IP的硬件逻辑图,主要由状态控制器、子密钥生成器、DES算法运算器三部分组成。其中,状态控制器用于控制IP的工作状态、模式和标识完成状态;子密钥生成器将56 bit密钥分成两部分,每部分按循环移位次数表移位并按置换选择表置换,从而生成每一轮次运算的子密钥K(K1,K2,…,K48);DES

基于FPGA技术的GPS数据加密系统设计研究,标签:eda技术,eda技术实用教程,http://www.88dzw.com

采用软件方式实现的DES算法会在很大程度上占用系统资源,造成系统性能的严重下降,而DES算法本身并没有大量的复杂数学计算(如乘、带进位的加、模等运算),在加密、解密过程和密钥生成过程中仅有逻辑运算和查表运算。因而,无论是从系统性能还是加、解密速度的角度来看,采用硬件实现都是一个理想的方案[3]。

图3为DES IP的硬件逻辑图,主要由状态控制器、子密钥生成器、DES算法运算器三部分组成。其中,状态控制器用于控制IP的工作状态、模式和标识完成状态;子密钥生成器将56 bit密钥分成两部分,每部分按循环移位次数表移位并按置换选择表置换,从而生成每一轮次运算的子密钥K(K1,K2,…,K48);DES算法运算器为整个IP的关键,它将64 bit中间数据分为左右两部分,分别记为Li和Ri。单个运算的过程可以写为下面的公式:

(1)将Ri-1按照扩展换位表E扩展为48 bit的数据;

(2)将扩展后的Ri-1与循环移位后的48 bit子密钥K(K1,K2,…,K48)“异或”;

(3)将“异或”后的结果送入8个S盒(S box)进行替代运算,每个S盒都有6 bit输入、4 bit输出,并且8个S盒都不相同,48 bit的输入分为6位一组,分别送到8个S盒选择相应的输出,结果为32 bit;

(4)S盒替代后的32 bit结果依照P盒(P box)进行置换,置换后结果即为f(Ri-1,Ki)的最终值,这样便完成了f函数的运算。

算法中用到的初始换位表IP、放大换位表E、替代函数表S、换位函数P、逆初始换位IP-1、密钥循环移位表可在参考文献[4]中查到。本设计中,GPS数据的加密在加密卡中完成,解密在服务器端完成,为方便功能扩展,在加密卡中设计、保留了解密功能。

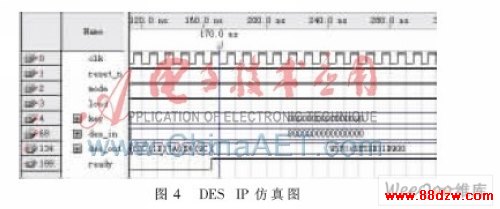

2.3 DES算法仿真验证

本设计的DES IP采用ALTERA公司的Quartus 7.0软件开发及Verilog HDL语言编写[5],整个加密卡在单片Cyclone系列EP1C6Q240C8N芯片上实现。图4为Quartus 7.0开发软件下DES IP的仿真图。

各仿真信号的意义及说明如下:

时钟信号(clk):周期为10 ns、占空比为50%;

复位信号(reset_n):低电平有效,置高;

模式信号(mode):加密/解密选择,‘1’为加密,‘0’为解密;

加载信号(load):高电平有效,置高;

加密数据(des_in):8000 0000 0000 0000;

密钥信号(key):0000 0000 0000 0000;

加密结果(des_out):95F8 A5E5 DD31 D900;

加密完成信号(ready) :在第17个周期后置高。

DES IP工作时,“密钥”保存在总线接口的密钥寄存器中,“加密数据”由NIOS输入,加密完成后,通过“加密完成信号”产生的I/O中断传回给NIOS。图4中,其加密结果与XILINX公司网站上设计参考中给出的数据一致,表明DES IP设计正确。

本设计采用FPGA技术设计了GPS数据加密系统,重点介绍了机载模块中DES IP的设计。实验发现,采用NIOS进行DES算法软件加密时速度慢,会出现间隔丢失GPS数据的现象,而采用硬件DES IP进行加密处理时,完全可以满足GPS接收机的速度需要,不会出现丢点现象。系统采用MD5算法对管理员口令进行加密,进一步增强了系统的安全性,因此本设计对解决该GPS测量系统安全性方面有较大的现实意义和实用价值。

- 上一篇:怎样改进SMT设备贴装率

《基于FPGA技术的GPS数据加密系统设计研究》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA技术的GPS数据加密系统设计研究

- 在谷歌中搜索相关文章:基于FPGA技术的GPS数据加密系统设计研究

- 在soso中搜索相关文章:基于FPGA技术的GPS数据加密系统设计研究

- 在搜狗中搜索相关文章:基于FPGA技术的GPS数据加密系统设计研究

当前位置:

当前位置: