基于AHB接口的高性能LCD控制器IP设计

[09-13 16:54:33] 来源:http://www.88dzw.com 接口定义 阅读:8851次

文章摘要:* LC_HS(LP):LCD的行同步信号,被用来锁存STN面板上的行数据。LP是高电平有效还是低电平有效是可以通过软件配置的。* LC_DE(ACD):LCD数据使能信号。该信号可以配置成每一帧切换或者每隔N行切换。* LC_PCLK:LCD输出的移位时钟,是让STN面板用来同步LCD输出的数据。LC_PCLK是高电平有效还是低电平有效是可以通过软件配置的。STN面板的接口时序LCD控制器通过LCD的数据总线持续的传送像素数据到LCD面板。总线的时序由LC_PCLK、LC_HS、LC_VS组成。LC_PCLK信号把像素数据打入到LCD面板内部的移位寄存器。LC_HS指示每一行的开始,LC_V

基于AHB接口的高性能LCD控制器IP设计,标签:接口技术,微机原理与接口技术,http://www.88dzw.com* LC_HS(LP):LCD的行同步信号,被用来锁存STN面板上的行数据。LP是高电平有效还是低电平有效是可以通过软件配置的。

* LC_DE(ACD):LCD数据使能信号。该信号可以配置成每一帧切换或者每隔N行切换。

* LC_PCLK:LCD输出的移位时钟,是让STN面板用来同步LCD输出的数据。LC_PCLK是高电平有效还是低电平有效是可以通过软件配置的。

STN面板的接口时序

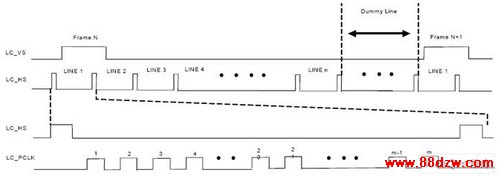

LCD控制器通过LCD的数据总线持续的传送像素数据到LCD面板。总线的时序由LC_PCLK、LC_HS、LC_VS组成。LC_PCLK信号把像素数据打入到LCD面板内部的移位寄存器。LC_HS指示每一行的开始,LC_VS则指示帧的第一行的开始。本LCD控制器可以支持绝大部分的单色LCD屏。图3解释了1位、2位、4位、8位LCD数据总线的接口时序。LC_HS信号再加上LC_VS信号表明了当前帧第一行的结束。在真实显示行中插入哑元行可以调节帧率。用户可以自己配置哑元行的数量。

图3 STN在8位, 4位, 2位以及1位数据宽度的接口时序。

LCD屏的宽度(PL)和高度(LF)寄存器里面定义了LCD面板的尺寸。LCD控制器将会以“LCD屏开始地址寄存器”(LCDImage0FrameBase)中的值为首地址来扫描显存,因此,被打上影音的区域将会最终显示在LCD面板上。

LCD虚拟页面宽度参数指定了最大显示页面宽度。通过修改LCDImage0FrameBase,可以使得真实显示的窗口大小和位置在虚拟页面边界的范围内变化。然后,对于编程人员来说,在软件设置定义显存扫描起地址的时候,是不能超多虚拟页面的高度和宽度,否则,屏幕上可能会有一些意想不到的景象。

这个IP在LCD屏的接口上还比一般的LCD控制器多了对串口RGB屏的支持,我们在FPGA开发板上就是使用AUO A036QN01串口RGB屏来验证。A036QN01的规格书上没有Dummy data(LCD Serial panel pixel Parameters: ffset=0200H),但我们的design是有dummy data跟没有dummy data的可以支持的。

IP内部的接口时钟关系

以上就这个IP的原理与子模块作了充分的说明, 再接着介绍IP内部的接口时钟关系。

FTLCDC200包含了三个时钟域分别为HCLK, LC_SCALER_CLK以及LC_CLK。HCLK时钟使用于AHB接口而且这个时钟与AHB接口是一致的。AHB必须为SoC上的LCD控制器提供足够的带宽用以由帧缓存区捕获足够的数据。

LC_SCALER_CLK提供时钟给scaler模块同时对scaler模块也要足够快来处理数据。LC_CLK用于产生像素时钟。像素时钟(LC_PCLK是由LC_CLK产生并且除以1, 2, 3等等。

此外, 这三个时钟域必须按照下面的两个原则才能运行顺畅:

? 1. HCLK ≥ LC_SCALER_CLK ≥ LC_CLK (频率)

? 2. LC_SCALER ≥ HCLK/16 (频率)

LC_CLK的频率变化依靠LCD屏的选择与使用。使用这个IP在频率上必须根据所选用的LCD屏的规格,下面两个例子介绍选择时钟频率的方法

范例1.

假设输入的分辨率是640x480, 每个在帧缓存区内的像素是16-bpp, AHB总线的带宽是32 bits, LCD屏的分辨率是320x240而显示的帧刷新率是30帧每秒。

在这个范例, scaling-down功能必须打开并且操作在1/2x1/2的步骤。

HCLK必须大于640x480 (输入的分辨率) x 16 (bpp) x 30 (帧刷新率)/32 (总线带宽) = 4.6 MHz

LC_SCALER_CLK必须大于640x480 (最大的 {输入的分辨率, 输出的分辨率}) x 30 (帧刷新率) = 9.2 MHz

LC_CLK必须大于320x240 (输出的分辨率) x 30 (帧刷新率) x 1.2 (门廊的空白) = 2.8MHz

因此, 针对这个范例, 使用者能选择以下的两个条件

HCLK ≥ LC_SCALER_CLK ≥ 9.2 MHz

LC_CLK ≥ 2.8 MHz

范例2.

假设输入的分辨率是640x480, 每个在帧缓存区内的像素是16-bpp, AHB总线的带宽是32 bits, LCD屏的分辨率是1280x960而显示的帧刷新率是30帧每秒。

在这个范例, scaling-down功能必须打开并且操作在2x2的步骤。

《基于AHB接口的高性能LCD控制器IP设计》相关文章

- › 基于AHB接口的高性能LCD控制器IP设计

- 在百度中搜索相关文章:基于AHB接口的高性能LCD控制器IP设计

- 在谷歌中搜索相关文章:基于AHB接口的高性能LCD控制器IP设计

- 在soso中搜索相关文章:基于AHB接口的高性能LCD控制器IP设计

- 在搜狗中搜索相关文章:基于AHB接口的高性能LCD控制器IP设计

当前位置:

当前位置: