基于USB2.0的轨道电路信号车载采集与分析系统

[09-13 16:55:35] 来源:http://www.88dzw.com 接口定义 阅读:8484次

文章摘要:2.3 FlF0的数据缓存作用由于A/D最高采样频率可达100MHz,而主控芯片CY7C68013中的FIFO只有4kB,不能满足A/D数据转换器的要求,因此需要在A/D和CY7-C68013之间增加一个高速的FIFO来缓存数据。FIFO是先进先出的数据缓存器,数据在其内部顺序写入、顺序读出,其数据地址由内部读写指针自动加1完成。它具有双口输入输出、采集传送速度快等特点,能满足高速数据传输的要求。由FIFO构成的数据缓冲电路主要部分的接口电路如图4所示。IDT7205有两种工作模式,即IDT标准模式和FWFT模式。本设计中采用IDT标准模式,这种模式通过FF、PAF、PAE、HF、EF五个标志

基于USB2.0的轨道电路信号车载采集与分析系统,标签:接口技术,微机原理与接口技术,http://www.88dzw.com2.3 FlF0的数据缓存作用

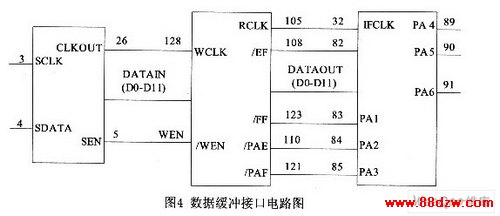

由于A/D最高采样频率可达100MHz,而主控芯片CY7C68013中的FIFO只有4kB,不能满足A/D数据转换器的要求,因此需要在A/D和CY7-C68013之间增加一个高速的FIFO来缓存数据。FIFO是先进先出的数据缓存器,数据在其内部顺序写入、顺序读出,其数据地址由内部读写指针自动加1完成。它具有双口输入输出、采集传送速度快等特点,能满足高速数据传输的要求。由FIFO构成的数据缓冲电路主要部分的接口电路如图4所示。

IDT7205有两种工作模式,即IDT标准模式和FWFT模式。本设计中采用IDT标准模式,这种模式通过FF、PAF、PAE、HF、EF五个标志位来实现数据的传输。/WEN(写使能端)置为有效时,数据可以写入FIFO。在WLCK(写时钟)的控制下,数据持续写入FIFO,当第一个数据被写入时,/EF(空标志)无效,数据不断地写入FIFO,即将写满时/PAE(将空标志)无效,/PAF(将满标志)有效,表示FIFO即将写满。当FIF0写满时,/FF(满标志)置为有效,控制A/D芯片停止写数。开始读数据时的第一个读操作使/FF置为无效,此时开始持续地读取数据,当FIFO中数据减少到一定程度,会使/PAF(将满)和/HF(半满)两个标志位置为无效,持续读出数据,而不写入数据;当FIFO中只剩下N个字时(N为空状态的缺省值),/PAF有效;当FIFO中的数据被全部读出时,/EF置为有效,此时控制主控芯片停止读取数据,与此同时A/D也开始下一个读取数据过程。

3 系统软件设计

3.1 固件设计

USB固件是运行在FX2芯片CY7C68013中的代码。在数据采集卡连接到计算机后,通过一个能自动完成固件下载以及设备重枚举功能的设备驱动程序,即固件下载驱动程序将USB固件下载到FX2的RAM中。

Cypress公司针对FX2系列的USB芯片给出了一个Firmware(固件)库,用户只需要在源程序中包含进EZUSB.H和EZREGS.H, 并且把EZU-SB.LIB和USBJMPB.OBJ添加进项目即可。

在设计中还利用了FX2的框架。FX2程序框架用于加速开发芯片外设。框架为FX2的初始化、处理设备标准USB设备请求以及USB挂起时的电源管理提供了现成的805l代码,只需简单地提供USB描述符表,编写完成外设功能的代码就可以开发一个功能完善的USB外设。

CY7C68013芯片的端点数总共有7个,根据设计需要,我们选择了其中的3个端点,其中1个控制端点、1个发送端点和1个接收端点。

3.2 驱动程序

在采集卡工作的运行WindowsxF台的主机上,Cypress公司提供了Windows下的通用驱动程序(GDP)。本采集卡使用这个通用驱动程序,不需要自己另行开发。

3.3 用户程序设计

用户程序设计部分则是基于C++Builder开发平台,设计并实现数据采集系统的功能。系统软件总体上包括数据采集(通道控制、触发控制)、波形显示、参数测量、频谱分析及波形存储与回放等五大模块。软件界面如图5所示。

3.3.1 数据采集模块

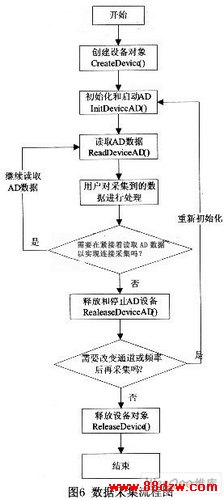

数据采集模块在整个系统中占有重要的地位,它是系统的核心。其工作流程图如图6所示,本模块主要完成通道控制、触发控制等功能。数据采集部分的参数设置正确与否,直接影响到后面的分析、处理、显示等功能能否实现。这部分的参数设置主要包括:

(1)通道控制。主要包括通道个数控制,系统提供的通道数为末通道数减去首通道数加1。

《基于USB2.0的轨道电路信号车载采集与分析系统》相关文章

- › 基于USB2.0的轨道电路信号车载采集与分析系统

- › 基于USB接口电路的远程电压监测系统

- › 基于USB2.0的高速图像传输系统设计

- › 基于USB2.0的红外数据传输系统的设计与实现

- › 基于USB传输及CMOS图像传感器的指纹识别仪的实现

- › 基于USB2.0的高分辨率数字摄像头设计

- 在百度中搜索相关文章:基于USB2.0的轨道电路信号车载采集与分析系统

- 在谷歌中搜索相关文章:基于USB2.0的轨道电路信号车载采集与分析系统

- 在soso中搜索相关文章:基于USB2.0的轨道电路信号车载采集与分析系统

- 在搜狗中搜索相关文章:基于USB2.0的轨道电路信号车载采集与分析系统

当前位置:

当前位置: