基于CPCI总线的多网口卡设计

[09-13 16:55:41] 来源:http://www.88dzw.com 接口定义 阅读:8856次

文章摘要:2.3.2 中断设计和IDSEL映射PCI2050B支持9个从设备,在初始化配置空间读写时,PCI2050B作为上一级PCI总线的操作对象,提供了IDSEL引脚进行器件选择,该引脚可以连接到高24位PCI总线中的任意一根。同时,为了减少地址线的容性负载,需要在该信号连线上串接一只1 kΩ的电阻。本模块仅扩展一级总线,PCI2050B主侧的IDSEL引脚直接连接到CPCI插座J1的IDSEL。对于二级总线侧的PCI器件(本模块为INTEL82551),其IDSEL引脚经过1 kΩ的电阻连接到PCI2050B的S_AD31S_ADl6引脚的任意一根。来自从侧上的设备的INT线不通过桥。如果桥位于一

基于CPCI总线的多网口卡设计,标签:接口技术,微机原理与接口技术,http://www.88dzw.com2.3.2 中断设计和IDSEL映射

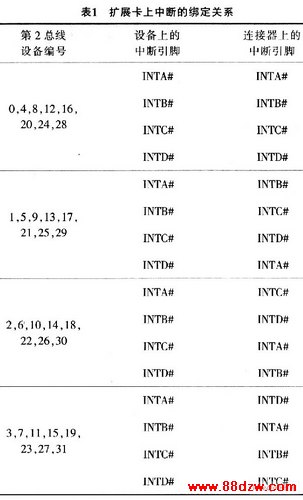

PCI2050B支持9个从设备,在初始化配置空间读写时,PCI2050B作为上一级PCI总线的操作对象,提供了IDSEL引脚进行器件选择,该引脚可以连接到高24位PCI总线中的任意一根。同时,为了减少地址线的容性负载,需要在该信号连线上串接一只1 kΩ的电阻。本模块仅扩展一级总线,PCI2050B主侧的IDSEL引脚直接连接到CPCI插座J1的IDSEL。对于二级总线侧的PCI器件(本模块为INTEL82551),其IDSEL引脚经过1 kΩ的电阻连接到PCI2050B的S_AD31S_ADl6引脚的任意一根。来自从侧上的设备的INT线不通过桥。如果桥位于一个插入卡上,从侧设备的中断线直接接到连接器的中断引脚(INTA#~INTD#)。本模块中,PCI2050B是一个桥设备,INTEL82551的中断引脚直接连接到J1的中断引脚。所有从设备的中断线的连接与设备编号(即IDSEL线的连接)有绑定关系,对应关系如表1所示。4片INTEL8255l的IDSEL引脚分别连接到S_AD28、S-AD29、S_AD30和S_AD31,对应的设备编号为12、13、14、15,则器件的中断引脚INT#对应连接到J1的INTA#、INTB#、INTC#、INTD#。

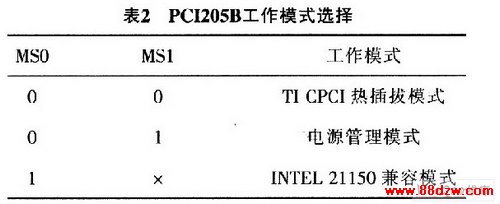

2.3.3 PCI2050B工作模式的选择

PCI2050B有3种工作模式可供选择:TI CPCI热插拔模式、电源管理模式和INTEL 21150兼容模式。选择引脚分别为MSO,MSl,模式选择定义如表2所示。

根据CPCI总线应用设计的需要,笔者选择了TI CPCI热插拔工作模式。当PCI2050B选择TI CPCI热插拔工作模式时,为了确保热插拔逻辑的正常工作,要求必须将HS_SWICH/GPI03引脚和HSENUM引脚上拉,同时,由于没有使用PCI2050B的关于GPI0引脚,且因为这些引脚在缺省条件下定义为输入脚,为了避免误触发,将这些引脚全部上拉。

3 以太网接口

本网卡使用4片INTEL82551、4片EEPROM 93C4*片PE68515实现4路以太网网络接口。INTEL82551是Intel公司的一款高集成的以太网控制器,其主要功能是实现以太网帧的收发。它集成了10Base-T/lOOBase-T MAC控制器和10Base-T/100Base-T PHY控制器,支持数据的全双工或半双工传输,支持自动协商,支持10/100 Mb/s传输速率,支持流控机制。

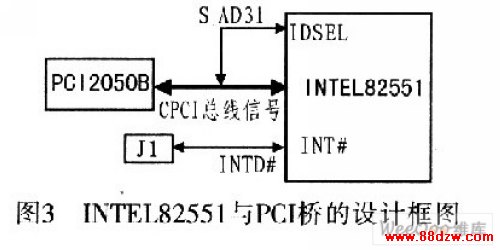

3.1 INTEL82551与PCI桥的接口设计

每片INTEL82551的CPCI总线信号连接到PCI2050B的从侧,应特别注意的是信号IDSEL和INT#根据表1一一对应,否则模块插到系统槽上,系统不能正确驱动模块。其中1路器件的电路连接,如图3所示。器件的IDSEL连接到S_AD31上,则器件的中断INT#连接到J1的INTD#上。

3.2 Intel82551与传输介质接口

使用4片PE68515和4个RJ-45实现传输介质接口。每一路接口电路连接,如图4所示。

3.3 网卡调试

PCB电装完后,检查各器件及其他电路是否有虚焊,网卡插于CPCI机箱插槽,在系统设备管理器中可看到模块属性,如IDSEL连接AD31,则属性为PCI SLOTl(PCI总线N,设备15,功能O)(N为总线编号)。用EEUPDATE对网卡配置后,模块可正常收发数据。

4 结束语

本四网口模块符合PCI2.2规范,已成功应用于3U CPCI机箱的Windows平台。根据需要可扩展为八网口的CPCI卡,此系列基于CPCI多网口卡,可广泛用于各类测试设备、有线通信等领域。

《基于CPCI总线的多网口卡设计》相关文章

- › 基于CPCI总线的多网口卡设计

- › 一种基于CPLD的声发射信号传输系统设计

- › 基于CPLD的臭氧电源控制系统的软硬件设计

- › 基于CPLD/FPGA的CMI编码设计与实现

- › 基于CPLD的压电生物传感器检测电路设计

- › 基于CPLD的CCD信号发生器的研究

- 在百度中搜索相关文章:基于CPCI总线的多网口卡设计

- 在谷歌中搜索相关文章:基于CPCI总线的多网口卡设计

- 在soso中搜索相关文章:基于CPCI总线的多网口卡设计

- 在搜狗中搜索相关文章:基于CPCI总线的多网口卡设计

当前位置:

当前位置: