千兆位设备PCB的信号完整性设计

[09-12 18:52:53] 来源:http://www.88dzw.com PCB设计 阅读:8951次

文章摘要:等效并联电导G也称为介质损耗(Dielectric Loss)。在低频时,等效并联电导与介质的体电导率和等效电容有关,而当频率升高时,介质损耗角开始起主导作用。此时介质电导率由介质损耗角和信号频率决定。一般来说,当频率小于1GHz时,趋肤效应损耗起主要作用,频率在1GHz以上时,介质损耗占据主导。在仿真软件中可以设置介电常数、介质损耗角、导体电导率以及截止频率,软件在仿真时会根据传输线的结构考虑趋肤效应与介质损耗的影响。如果仿真衰减,一定要根据信号的带宽设置相应的截止频率,带宽由信号边沿速率决定,许多622MHz信号与2.5GHz信号边沿速率差别不大,另外在有损传输线的模型中也可以看到等效电阻

千兆位设备PCB的信号完整性设计,标签:pcb培训,pcb是什么,pcb软件,http://www.88dzw.com

等效并联电导G也称为介质损耗(Dielectric Loss)。在低频时,等效并联电导与介质的体电导率和等效电容有关,而当频率升高时,介质损耗角开始起主导作用。此时介质电导率由介质损耗角和信号频率决定。

一般来说,当频率小于1GHz时,趋肤效应损耗起主要作用,频率在1GHz以上时,介质损耗占据主导。

在仿真软件中可以设置介电常数、介质损耗角、导体电导率以及截止频率,软件在仿真时会根据传输线的结构考虑趋肤效应与介质损耗的影响。如果仿真衰减,一定要根据信号的带宽设置相应的截止频率,带宽由信号边沿速率决定,许多622MHz信号与2.5GHz信号边沿速率差别不大,另外在有损传输线的模型中也可以看到等效电阻和电导随频率变化而不同。

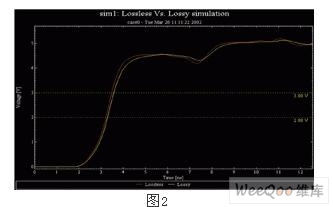

从图2中可看出,损耗使信号的上升沿变缓,即减小了信号的带宽,并且损耗减小了信号的幅度。从另一方面讲,这对于抑制信号过冲是有好处的。

传输线的串扰也会影响损耗,串扰决定于传输线物理结构、耦合长度、信号强度和边沿速率。在一定长度后串扰会饱和,损耗却不一定增加。

过孔和连接器的影响

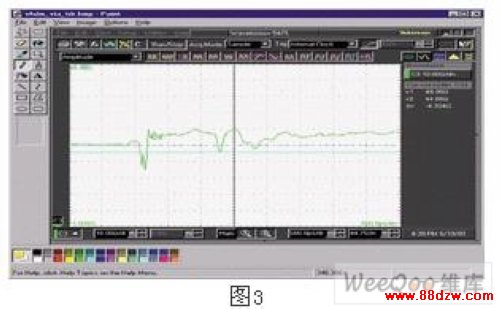

过孔将信号输送到板子的另一侧,板间的垂直金属部分是不可控阻抗,而且从水平方向变为垂直方向的拐点是一个断点,会产生反射,应尽量减少它的出现(图3)。

在千兆位系统设计仿真中,要考虑过孔的影响,需要有过孔模型。过孔的模型结构为串连电阻R、电感L和并联电容C形式。根据具体应用和精度要求,可以采用多个RLC结构并联的形式,并考虑与其它导体间的耦合,此时过孔模型就是一个矩阵。

过孔模型的获取有两种方法,一种是通过测试例如通过TDR来获得,另一种可以通过3D的场提取器(Field Solver)根据过孔的物理结构来提取。

过孔模型参数与PCB的材料、叠层、厚度、焊盘/反焊盘尺寸、以及与其连接的连线的连接方式有关。在仿真软件中,根据精度要求可以设置不同的参数,软件会依据相应的算法提取过孔的模型并在仿真时考虑其影响。

在千兆位系统PCB的设计中尤其要考虑连接器的影响,现在高速连接器技术的发展已经可以很好地保证信号传输时阻抗与地平面的连续性,设计中对连接器的仿真分析主要采用多线模型。

连接器多线模型是在三维空间下,考虑管脚间的电感和电容耦合提取出来的模型。连接器多线模型一般使用三维场提取器提取出RLGC矩阵,一般是Spice模型子电路形式。由于模型结构复杂,提取和仿真分析时都需要较长的时间。在SpecctraQuest软件中,可以把连接器的Spice模型编辑成Espice模型,赋给器件或直接调用,也可以编辑成DML格式的封装模型赋给器件使用。

差分信号及布线考虑

差分信号具有抗干扰强、传输速率高的优点,在千兆位信号传输中,可以更好降低串扰、EMI等的影响,其耦合形式有边沿耦合与上下耦合、松耦合和紧耦合等形式。

边沿耦合与上下耦合相比具有更好降低串扰、布线方便、加工简单等优点,上下耦合更经常应用于布线密度大的PCB 板。紧耦合相对于松耦合具有更好的抗干扰能力,并能减小串扰,松耦合则可更好控制差分走线阻抗的连续性。

具体的差分走线规则要根据不同的情况考虑阻抗连续性、损耗、串扰、走线长度差异等的影响。差分线最好用眼图来分析仿真结果。仿真软件可以设定随机序列码产生眼图,并且可以输入抖动与偏移参数分析其对眼图的影响。

《千兆位设备PCB的信号完整性设计》相关文章

- › 千兆位设备PCB的信号完整性设计

- 在百度中搜索相关文章:千兆位设备PCB的信号完整性设计

- 在谷歌中搜索相关文章:千兆位设备PCB的信号完整性设计

- 在soso中搜索相关文章:千兆位设备PCB的信号完整性设计

- 在搜狗中搜索相关文章:千兆位设备PCB的信号完整性设计

当前位置:

当前位置: