控压型DC-DC变换器电流环路补偿设计

[10-10 20:39:48] 来源:http://www.88dzw.com 电源电路 阅读:8869次

文章摘要:显然,要使环路稳定,必须使△I1<△Io,即满足:www.88dzw.com最后,VSEN’经过V/I转换电路,就可以转换成所需要的电流信号ISEN,以便和ISLOPE进行叠加。因为图4中的Q1和Q2匹配,偏置相同,所以Q1和Q2的发射极电压近似相等,即:V2≈V3,因而可为v∑提供一个合适的直流电平。4 仿真结果采用0.6μm BCD工艺时,可对设计的电路进行仿真验证。仿真条件为供电电压VIN=5 V,输出电压VOUT=13 V,负载电流为500 mA。由仿真条件可知,占空比D>50%,但必须引入斜坡补偿以保证电流环路的稳定。图5所示是整体电路在典型情况下(D>50%),加

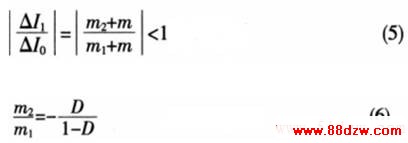

控压型DC-DC变换器电流环路补偿设计,标签:电源电路,电路设计,http://www.88dzw.com显然,要使环路稳定,必须使△I1<△Io,即满足:

www.88dzw.com

www.88dzw.com最后,VSEN’经过V/I转换电路,就可以转换成所需要的电流信号ISEN,以便和ISLOPE进行叠加。

因为图4中的Q1和Q2匹配,偏置相同,所以Q1和Q2的发射极电压近似相等,即:V2≈V3,因而可为v∑提供一个合适的直流电平。

4 仿真结果

采用0.6μm BCD工艺时,可对设计的电路进行仿真验证。仿真条件为供电电压VIN=5 V,输出电压VOUT=13 V,负载电流为500 mA。由仿真条件可知,占空比D>50%,但必须引入斜坡补偿以保证电流环路的稳定。

图5所示是整体电路在典型情况下(D>50%),加入斜坡补偿的仿真波形。其中,图5(a)是电感实际的电流波形。其电感电流峰值为Iinductor_PEAK=1.796 A;图5(b)是采样得到的电感电流波形,其采样电感电流峰值为Isensc_PEAK=10.505μA。

由于设计中的典型值R2=R3=10 kΩ,RDS(MM)=150 mΩ,RDS(MS)=15 Ω,n=100,故其电流采样系数α为:7.5x10-6,采样精度为77.9%。

图5(c)是斜坡补偿电路产生的斜坡电流波形,实测的补偿斜坡的斜率为5.487 A/s,时钟CLK为1.2 MHz,占空比为85.7%,T1=685.563 ns。由于本设计中的典型值为:

V1=0.4 V,V2=1 V,R=65 kΩ。

故可得其补偿斜坡的斜率为:m=6.732 A/s。

因此可知,本设计的补偿斜坡已经达到较高精度(81.5%),可以满足设计要求;

图5(d)是电感电流采样值与补偿斜坡的合成波形。可以看出,其斜坡补偿的加入有效的抑制了亚谐波振荡。

5 结束语

本文针对峰值电流模式DC-DC转换器固有的不稳定性,设计了斜坡补偿电路。采用固定斜率补偿技术,虽然在小占空比条件下会减弱电流模式PWM控制的优点,但其电路结构简单,容易调节,可降低设计难度,同时针对一般的便携式设备,完全可以满足应用要求;而电流采样电路使用SENSE FET,同时结合缓冲级和V/I转换电路,可在采样精度得到提高的同时减小损耗。因此,本设计中的两个V/I转换电路可以较好地移植到其它DC-DC变换器电路中。

目前,本电路已经应用在一款升压型DC-DC芯片中,并且已经完成了前期仿真。仿真结果达到了预期要求,证明了该电路的可行性。 www.88dzw.com

结合(5)和(6)两个式子可以得到:

由此可见,当时,可在最坏情况下(D=100%,即m2>>m1)满足系统的开环稳定性要求。

图1所示的电路同时给出了在电流反馈电压上叠加斜坡补偿电压的方法。通过比较分析可知,两种补偿方法在效果上是等效的,但是第二种方法中的电路实现相对更简单,因此较为常用。

2.2 电流采样原理与方法

传统电流采样方法是在开关管的电流通路上串接检测电阻,这样不仅降低了DC-DC转换器的效率,而且对于传统工艺来说,制作这样的小电阻也很困难。为了弥补这些不足,本文在SENSEFET采样方法的基础上,加入了简洁的V/I变换电路,从而形成了一种结构简单且精度较高的采样电路,其电路主体如图l中的采样电路所示。其中MM为POWER FET,其宽长比设计的非常大,可以减小其导通阻抗(本电路的典型值为150 mΩ);Ms为SENSE FET;检测电阻RSEN可利用工作在线性区MOS管的导通阻抗特性,使其宽长比与Ms相同,因此,导通阻抗与Ms的相等,记为RSEN。为了减小采样损耗,一般必须使(W/L)MM<<(W/L)Ms。

Tag:电源电路,电源电路,电路设计,家电维修 - 单元电路介绍 - 电源电路

《控压型DC-DC变换器电流环路补偿设计》相关文章

- › 控压型DC-DC变换器电流环路补偿设计

- 在百度中搜索相关文章:控压型DC-DC变换器电流环路补偿设计

- 在谷歌中搜索相关文章:控压型DC-DC变换器电流环路补偿设计

- 在soso中搜索相关文章:控压型DC-DC变换器电流环路补偿设计

- 在搜狗中搜索相关文章:控压型DC-DC变换器电流环路补偿设计

最新更新

当前位置:

当前位置: