TMS320F2812与CPLD的视频采集系统接口设计

[10-10 20:38:44] 来源:http://www.88dzw.com 单片机学习 阅读:8659次

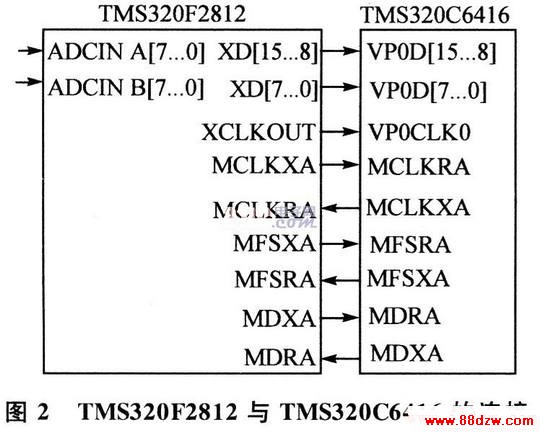

文章摘要: CPLD控制模块。主要实现系统的逻辑控制和存储器地址译码功能。CPLD将经过同步分离后的行、场同步信号转换成YUV422格式的数字信号,同时产生SDRAM的地址、读写选通等信号。由CPLD输出的YUV422格式的数字信号按像素逐个存入2片存储器中,其中2片SDRAM以乒乓方式工作。这里CPLD选用Altera公司的EPM7128芯片。 DSP图像处理与显示接口模块。选用TI公司的DSP芯片TMS320C6416。该芯片有HPI和EMIF接口,2个外部总线接口EMIF-A和EMIF-B的时钟为100MHz,2片存储器被映射到这2个总线上。其中,SDRAMA映射到EMIF-A,256

TMS320F2812与CPLD的视频采集系统接口设计,标签:单片机开发,单片机原理,http://www.88dzw.com

CPLD控制模块。主要实现系统的逻辑控制和存储器地址译码功能。CPLD将经过同步分离后的行、场同步信号转换成YUV422格式的数字信号,同时产生SDRAM的地址、读写选通等信号。由CPLD输出的YUV422格式的数字信号按像素逐个存入2片存储器中,其中2片SDRAM以乒乓方式工作。这里CPLD选用Altera公司的EPM7128芯片。

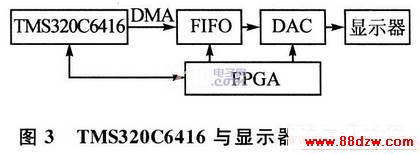

DSP图像处理与显示接口模块。选用TI公司的DSP芯片TMS320C6416。该芯片有HPI和EMIF接口,2个外部总线接口EMIF-A和EMIF-B的时钟为100MHz,2片存储器被映射到这2个总线上。其中,SDRAMA映射到EMIF-A,256 MB,64位宽,800 MB/s的瞬时突发率;SDRAMB映射到EMIF-B,8 MB,16位宽,200 MB/s的瞬时突发率。可以方便地与其他处理器连接,有实时的硬件调试功能。开发工具包含CCS环境、DSP BIOS、JTAG扫描控制器等。CPLD写完一帧图像后发中断信号通知DSP读取,DSP执行中断服务程序从SRAM中将一帧图像读入,随即进行处理。其模块与显示器接口的连接如图3所示。

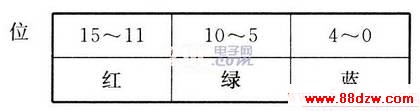

FPGA用于对FIFO的读/写时序与逻辑控制。FIFO的写时序信号由TMS320C6416的EMIF外部总线产生。通过DMA方式将视频数据写入FIFO缓存器中,再通过DAC输出视频编码器将YUV422格式的数字信号转换成SVGA格式的RGB信号格式,并将它输出到显示器上。输出VGA分辨率为800×600(SVGA制),但在TMS320C6416存储器中的像素格式为RGB565。每个像素存储在16位的存储器中,其SVGA输出像素格式的存储方式如下:

Tag:单片机学习,单片机开发,单片机原理,维修教程知识 - 单片机学习

《TMS320F2812与CPLD的视频采集系统接口设计》相关文章

- › 基于TMS320LF2407A DSP的PFC级电路的原理与设计

- › 基于TMS320F2812变频电源的交流采样系统设计

- › 基于TMS320DM642的电视跟踪系统设计

- › 用TMS320DM270在MP4上实现GPS导航

- › TMS320C5402 在电视数字传输复用器中的应用

- › TMS320F2812与CPLD的视频采集系统接口设计

- 在百度中搜索相关文章:TMS320F2812与CPLD的视频采集系统接口设计

- 在谷歌中搜索相关文章:TMS320F2812与CPLD的视频采集系统接口设计

- 在soso中搜索相关文章:TMS320F2812与CPLD的视频采集系统接口设计

- 在搜狗中搜索相关文章:TMS320F2812与CPLD的视频采集系统接口设计

最新更新

当前位置:

当前位置: