多串口单一中断源的芯片设计

[10-10 20:38:44] 来源:http://www.88dzw.com 单片机学习 阅读:8245次

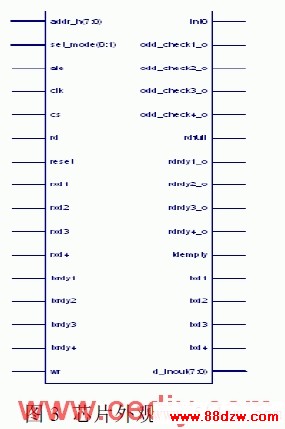

文章摘要:9600bps,则 clk的频率是 9600×4=38400Hz。4、cs:芯片总片选信号输入引脚,低电平有效。5、rd,wr:单片机向芯片读写的控制引脚,低电平有效。6、rxd1,rxd2,rxd3,rxd4:串行输入引脚。7、INT0:中断信号输出引脚,下降沿有效。8、odd_check1_o,odd_check2_o,odd_check3_o,odd_check4_o:送给单片机的奇偶校验标志信号输出引脚。 9、rdfull:数据缓冲器标志信号输出引脚,该信号用‘1’和‘0’表明是否有收发器的缓存了数据尚未被提取。10、rdrdy1,rdrdy2,rdrdy3,rdrdy4:引脚分别用于

多串口单一中断源的芯片设计,标签:单片机开发,单片机原理,http://www.88dzw.com9600bps,则 clk的频率是 9600×4=38400Hz。

4、cs:芯片总片选信号输入引脚,低电平有效。

5、rd,wr:单片机向芯片读写的控制引脚,低电平有效。

6、rxd1,rxd2,rxd3,rxd4:串行输入引脚。

7、INT0:中断信号输出引脚,下降沿有效。

8、odd_check1_o,odd_check2_o,odd_check3_o,odd_check4_o:送给单片机的奇偶校验标志信号输出引脚。

9、rdfull:数据缓冲器标志信号输出引脚,该信号用‘1’和‘0’表明是否有收发器的缓存了数据尚未被提取。

10、rdrdy1,rdrdy2,rdrdy3,rdrdy4:引脚分别用于表明各个收发器是否正忙,从该收发器开始接收数据到数据被单片机读取整个过程,其相应的rdrdy引脚输出‘1’。

11、txd1,txd2,txd3,txd4:串行数据输出引脚。

12、tdempty:该引脚输出为‘1’时表明芯片已没有正在发送或者是将要发送的数据。

13、txrdy1,txrdy2,txrdy3,txrdy4:分别为收发器 1、2、3和 4可否进行发送控制输入端,输入为‘1’表示可以进行串行数据的发送。

14、d_inout(7:0):双向数据总线。应与单片机 p0口相连。

15、addr_h(7:0):地址高 8位。

4程序的综合及仿真

4.1 设计综合及实现

本设计综合使用的工具是 Xilinx公司的 XST,它是内嵌在 ISE7.2i里面的。综合过程将把软件设计的 HDL描述与硬件结构挂钩,是将软件转化为硬件电路的关键步骤 [7-9]。本设计综合时选用的芯片是Spartan-ⅡE系列的xc2s100e。

综合工具生成网表文件后,就可以实现设计,实现的步骤有:转换(将多个设计文件合并为一个网表),映射(将网表中的逻辑符号(门)整合到物理元件中),布局布线(将元件放到器件中,并将它们连接起来,同时提取出时序数据,并生成各种报告)。

4.2 综合布线结果及分析

图 4为资源利用结果图表,由图可见,slices的占用量为 722个,占该芯片 slices总数的 60%。slice registers的使用数量为 591个,占该芯片总数的 24%。4输入查找表的使用总量是 915个,占该芯片查找表总数的 38%。

4.3 布线后仿真

本文中所举出的测试均为布线后的仿真测试,该仿真的仿真延时文件包含的延时信息最全,不仅包含了门延时,还包含了实际布线延时,所以布局布线后仿真最准确,能够较好的反映芯片的实际工作情况。

Tag:单片机学习,单片机开发,单片机原理,维修教程知识 - 单片机学习

《多串口单一中断源的芯片设计》相关文章

- › 多串口单一中断源的芯片设计

- 在百度中搜索相关文章:多串口单一中断源的芯片设计

- 在谷歌中搜索相关文章:多串口单一中断源的芯片设计

- 在soso中搜索相关文章:多串口单一中断源的芯片设计

- 在搜狗中搜索相关文章:多串口单一中断源的芯片设计

最新更新

当前位置:

当前位置: