基于MIPS内核的HDTV-SoC平台总线接口模块

[10-10 20:36:41] 来源:http://www.88dzw.com 电子制作 阅读:8426次

文章摘要: 图3 FIFO机制逻辑框图 双口RAM读写模块在与系统总线的接口逻辑方面,RAM读写模块与寄存器读写模块是类似的,这里不再赘述。不同之处在于与外部模块的接口逻辑,寄存器读写模块是采用直接连线的方式,而RAM读写模块则必须满足相应的双口RAM的接口时序。在本设计中,选用了SMIC的0.18µm库的双口RAM单元作为模型。该模型的接口时序如图4所示,包括了读时序和写时序两种情况。 图4 双口RAM接口时序图 中断控制模块 中断控制模块负责处理由DeMux

基于MIPS内核的HDTV-SoC平台总线接口模块,标签:电子小制作,http://www.88dzw.com

图3 FIFO机制逻辑框图

双口RAM读写模块

在与系统总线的接口逻辑方面,RAM读写模块与寄存器读写模块是类似的,这里不再赘述。不同之处在于与外部模块的接口逻辑,寄存器读写模块是采用直接连线的方式,而RAM读写模块则必须满足相应的双口RAM的接口时序。在本设计中,选用了SMIC的0.18µm库的双口RAM单元作为模型。该模型的接口时序如图4所示,包括了读时序和写时序两种情况。

图4 双口RAM接口时序图

中断控制模块

中断控制模块负责处理由DeMux、VD、GPIO等外部模块的中断源所发出的中断,对于系统来说,如何使产生的中断尽快得到响应是一个关键的问题。在图1中可以看到MIPS4Kc处理器所提供的中断引脚的连接情况,有关其引脚的说明如表1所示[1]。

表1 MIPS4Kc处理器中断引脚描述表

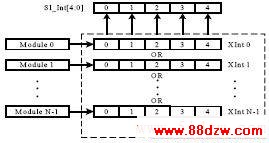

习惯将SI_TimerInt信号接到SI_Int[5]引脚,就像图1中所显示的那样。这样4Kc处理器的外部中断引脚就剩下5根,即SI_Int[4:0]。在本设计中,将系统外部中断分为5级,按照SI_Int[0]到SI_Int[4]的顺序优先级从高到低排列。针对每个外部模块,也将其所有的中断源分为5级,反映到每个模块的输出是一个5比特的寄存器XInt[4:0],同样,按照XInt[0]到XInt[5]的顺序中断优先级从高到低排列。假设系统有N个外部模块,则各个模块输出的XInt之间相或即得到SI_Int的输入,这些逻辑在TopInt模块中实现,如图5所示。

图5 TopInt模块内部逻辑

需要说明的是,TopInt模块本身也被当作系统的一个外部模块,系统可以对其进行与其它模块相同的寄存器读写操作。这样CPU在处理外部中断时,就可以通过读取XIntn寄存器的内容,追溯中断的产生源。另外,在每一个外部模块内部,设置5个32位的中断请求寄存器IRQREG0~IRQREG4和5个32位的中断屏蔽寄存器MSKREG0~MSKREG4。当MSKREGn寄存器中的某个比特位被置“1”时,则IRQREGn寄存器中相应比特位的中断被屏蔽。在每一个IRQREGn寄存器当中,32个比特位之间相或即得到该模块相应XInt寄存器中的第n比特位的值。由此也可以看出,按照IRQREG0到IRQREG4的顺序,中断优先级从高到低。它们之间的逻辑关系如图6所示。

- 上一篇:智能手机的系统架构及其低功耗设计

《基于MIPS内核的HDTV-SoC平台总线接口模块》相关文章

- › 基于MIC3203设计的HBLED驱动方案

- › 基于MIC2826设计的四输出可编电源管理方案

- › 基于MIC3263设计的六路LED驱动技术

- › 基于MIPS内核的HDTV-SoC平台总线接口模块

- 在百度中搜索相关文章:基于MIPS内核的HDTV-SoC平台总线接口模块

- 在谷歌中搜索相关文章:基于MIPS内核的HDTV-SoC平台总线接口模块

- 在soso中搜索相关文章:基于MIPS内核的HDTV-SoC平台总线接口模块

- 在搜狗中搜索相关文章:基于MIPS内核的HDTV-SoC平台总线接口模块

当前位置:

当前位置: