新型数字CCD相机及其图像数据传输卡设计

[09-14 01:02:23] 来源:http://www.88dzw.com 电子制作 阅读:8292次

文章摘要:lpm_ff_component3.clock = FVALT&STROBT&LVALT&GP5 # GP5&VCLKlpm_ff_component3.data0..0 = VSYNNSTROO = FVALT&STROBT&LVALT&GP5A19..0 = lpm_counter_component.q19..0lpm_counter_component.aclr = sclrlpm_counter_component.clock=FVALT&STROBT&LVALT&GP5 # GP5&VCLK/WE = FVALT&LVALT&STROO

新型数字CCD相机及其图像数据传输卡设计,标签:电子小制作,http://www.88dzw.comlpm_ff_component3.clock = FVALT&STROBT&LVALT&

GP5 # GP5&VCLK

lpm_ff_component3.data0..0 = VSYNN

STROO = FVALT&STROBT&LVALT&GP5

A19..0 = lpm_counter_component.q19..0

lpm_counter_component.aclr = sclr

lpm_counter_component.clock=FVALT&STROBT&LVALT&

GP5 # GP5&VCLK

/WE = FVALT&LVALT&STROO

/OE = FVALT

FVTA = FVALT

/FVTA = FVALT

VCLK = lpm_counter_component1.q0..0

lpm_counter_component1.clock = VVCLK

VVCLK = CLK & GP5

2VCLK = VVCLK

F1 = A19&GP5

HSYNN =A5&A6&A7&A8&A9&GP5

VSYNN =A14&A15&A16&A17&A18&GP5

END

2.3 多层高速印制电路板设计

笔者研制的图像数据传输卡的印制板设计为四层板,除了顶层和低层外,单独设计了电源和地层,这是基于PCI总线板卡的基本要求。另外,由于卡上的数据、地址及控制信号多为高速信号,在进行印制板设计时,还必须注意以下几点:

·PCI桥引脚的最大走线长度限于1.5英寸,CLK信号走线长度限于2.5±0.1英寸,且只连接一个负载;

·板上的共享PCI信号线的无负载特性阻抗(Z0)应控制在60~100Ω;

·PCI控制信号应考虑上拉电阻;

·每个电源引脚都要对地去耦合,处理开关电流的冲击。一般跨接0.01μF高频去耦电容;

·采集卡应遵守最大引脚电容小于10pF的限制;

·共享的PCI信号在板上,只能带一个负载。

在深入研究了数字CCD相机接口要求的基础上,按照以上的设计原理,自行研制成功基于PCI总线的、适用于多相机同时曝光的图像数据传输卡。该卡在机载多波段偏振成像系统原理样机中成功地通过了调试。测试数据表明,图像数据传输卡能够满足系统的设计要求。

www.88dzw.com

2 数字CCD相机图像数据传输卡的设计实现

在应用系统中,数字CCD相机图像数据传输卡的主要任务是产生相机工作所需的输入信号,解译相机的输出信号,使相机在电控方式下工作并实时、正确地抓取相机输出的图像数据,在相机和计算机内存之间建立硬件传输通道。为了适应数字CCD相机数据传输速率的不断提高,早期基于ISA总线的图像数据传输卡正逐步向基于PCI总线的传输卡过渡。

2.1 图像数据传输卡电路说明

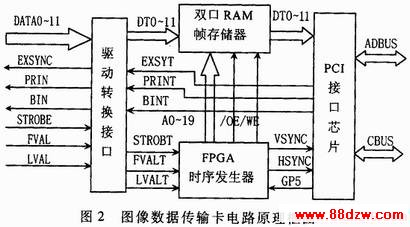

笔者设计开发的适用于DALSA公司CA-D7-1024T型数字CCD相机的图像传输卡的原理框图如图2所示。

驱动转换接口电路对相机与传输卡间的接口信号进行RS422和TTL电平间的相互转换;双口RAM为帧存储器,经编程控制可将相机输出的一帧图像数据写入,或经PCI桥读出图像数据至内存。采用帧存储器可以实现多个相机同时曝光,图像数据分时通过计算机总线写入内存。FPGA时序发生器用来产生双口RAM的地址线、读写控制线以及相机和传输卡正常工作所需的联络信号。PCI接口芯片是计算机与双口RAM及FPGA间的桥梁,在它们之间实现数据、控制信号的传输,并可通过初始化设置,实现PCI协议提供的各种传输模式。

2.2 FPGA时序逻辑发生器设计

本图像数据传输卡采用ALTRA公司生产的FPGA芯片EPM7128SLC84-15作为时序逻辑发生器。通过在系统编程(ISP)使其实现一个20位计数器、一个1位计数器、两个锁存器及十几个非标逻辑门的功能。其中20位计数器给1M×4Bit的帧存储器提供地址;1位计数器用来对卡上的30MHz时钟信号进行二分频,产生15MHz的VCLK信号;两个锁存器分别输出行同步和场同步信号;逻辑门用来实现信号的与、或、非等逻辑运算。

ALTERA公司的MAX+PLUSⅡ编程仿真工具软件,可对FPGA芯片进行在系统编程、仿真、调试,大大提高了传输卡设计的灵活性和对不同型号相机的适应能力,缩短了传输卡的研发周期。使用AHDL编程语言对FPGA芯片进行在系统编程,程序文件的主体如下:

BEGIN

HSYNC = lpm_ff_component2.q0..0

lpm_ff_component2.clock = FVALT&STROBT&LVALT&

GP5 # GP5&VCLK

lpm_ff_component2.data0..0 = HSYNN

VSYNC = lpm_ff_component3.q0..0

《新型数字CCD相机及其图像数据传输卡设计》相关文章

- › 新型数字示波器应用问答

- › 新型数字CCD相机及其图像数据传输卡设计

- 在百度中搜索相关文章:新型数字CCD相机及其图像数据传输卡设计

- 在谷歌中搜索相关文章:新型数字CCD相机及其图像数据传输卡设计

- 在soso中搜索相关文章:新型数字CCD相机及其图像数据传输卡设计

- 在搜狗中搜索相关文章:新型数字CCD相机及其图像数据传输卡设计

编辑推荐

- · 自制教室照明节电控制器

- · 双色音乐彩灯的制作

- · 三相交流电机缺相保护器

- · 声光控节能灯的制作

- · 同线电话转呼及互通器电路

- · 超低频信号发生器的制作

- · 自制热转印电路板

- · 警笛发声生器电路

- · 一款节能电路

- · 利用太阳能充电的旅行充电器

当前位置:

当前位置: