EPM570在视频采集中的设计与应用

[09-14 01:02:44] 来源:http://www.88dzw.com 电子制作 阅读:8278次

文章摘要:4.2 SRAM数据控制数据线控制电路主要由4个8位三态缓冲门组成,如图3所示。其中VP0~VP7为SAA7113的8位数据输出,其原理与地址线控制电路类似。写控制电路由2个4输入或门构成,其中nHREF及nVREF由HREF、VREF取非得到,实现只有在有效数据时才形成写使能WE。5 系统仿真从图4所示的Quartus II时序分析中可以看出LLC与ODD_nWE的延迟为8.8 ns,ODD_nWE与计数器生成的地址线的时间间隔为10 ns,即地址线的生成与LLC上升沿的时延为18.8 ns,由于LLC为27 MHz半个周期为18.5 ns,本系统设计正好满足SAA7113输出数据在LLC的

EPM570在视频采集中的设计与应用,标签:电子小制作,http://www.88dzw.com4.2 SRAM数据控制

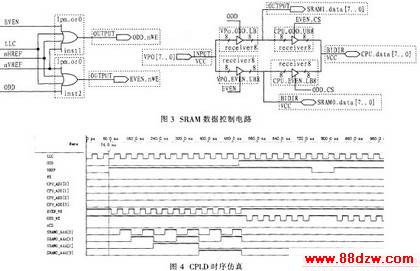

数据线控制电路主要由4个8位三态缓冲门组成,如图3所示。其中VP0~VP7为SAA7113的8位数据输出,其原理与地址线控制电路类似。写控制电路由2个4输入或门构成,其中nHREF及nVREF由HREF、VREF取非得到,实现只有在有效数据时才形成写使能WE。

5 系统仿真

从图4所示的Quartus II时序分析中可以看出LLC与ODD_nWE的延迟为8.8 ns,ODD_nWE与计数器生成的地址线的时间间隔为10 ns,即地址线的生成与LLC上升沿的时延为18.8 ns,由于LLC为27 MHz半个周期为18.5 ns,本系统设计正好满足SAA7113输出数据在LLC的下降沿开始有效。两片SRAM地址信号SRAM0_Add、SRAM1_Add以及SRAM写信号ODD_nWE、ENEN_nWE随着场同步信号ODD交替出现,实现了高效的乒乓切换混存结构。

6 结束语

本文采用EPM570与两片512 KB SRAM实现视频采集系统,相较于采用双口RAM、高速FIFO的缓存结构不仅价格低廉,能在时序上进行控制,还能获得720×576的实际有效分辨率,缓存效率高,占用处理器资源少。为处理器进一步进行视频压缩提供了有力的保障。

3.1 MAX II器件优点

MAX II系列器件主要有以下优点:

成本优化的架构。四倍的密度,一半的价格(和上一代MAX器件相比)。以最小化裸片面积为目标的架构,业界单个I/O引脚成本最低;

低功耗。十分之一的功耗(和3.3 V MAX器件相比)。1.8 V内核电压以减小功耗,提高可靠性。

支持内部时钟频率高达300 MHz:两倍的性能(和3.3 V MAX器件相比);

内置用户非易失性Flash存储器。通过取代分立式非易失性存储器件减少元件数;

实时在系统可编程能力(ISP)。器件在工作状态时能够下载第二个设计,降低远程现场升级的成本;

片内电压调整器支持3.3 V、2.5 V或1.8 V电源输入。减少电源电压种类,简化单板设计;

多电压提供能力和外部器件在1.5 V、1.8 V、2.5 V或3.3 V逻辑级的接口。施密特触发器、回转速率可编程以及驱动能力可编程提高了信号完整性。

Altera提供免费的Quartus II基础版软件,支持所有MAX II器件,它是基于MAX II器件引脚锁定式装配和性能优化而设计的。

3.2 EPM570T144C5

本系统采用的切换电路逻辑相对比较简单,而所需要的GPIO较多,同时为了与SRAM及处理器电压匹配,所以选用核心电压3.3 V、144引脚(其中116个GPIO)的EPM570T144C5作为实现控制电路的CPLD。

EPM570T144C5内部有570个逻辑单元(Logic Element),相当于440个宏单元(Macrocell),此前常用的EPM7128只有128个宏单元。EPM570T144C5内部分为两个I/O bank,共116个通用I/O,引脚延时为8.8ns。满足系统的设计要求。

4 具体实现

本系统选用IS61LV5128AL为缓存使用的SRAM,该器件容量为8 bit 512 KB,有8条地址线(I/O0~I/O7)、19条地址线(A0~18)、片选使能CE(低电平有效)、输出使能OE(低电平有效)、写使能WE(低电平有效)。由于两片SRAM需要一直工作,且当写有效时(WE低电平)是输出使能无效,所以CE与OE可一直保持低电平,写控制由CPLD生成。

《EPM570在视频采集中的设计与应用》相关文章

- › EPM570在视频采集中的设计与应用

- 在百度中搜索相关文章:EPM570在视频采集中的设计与应用

- 在谷歌中搜索相关文章:EPM570在视频采集中的设计与应用

- 在soso中搜索相关文章:EPM570在视频采集中的设计与应用

- 在搜狗中搜索相关文章:EPM570在视频采集中的设计与应用

编辑推荐

- ・ 自制教室照明节电控制器

- ・ 双色音乐彩灯的制作

- ・ 三相交流电机缺相保护器

- ・ 声光控节能灯的制作

- ・ 同线电话转呼及互通器电路

- ・ 超低频信号发生器的制作

- ・ 自制热转印电路板

- ・ 警笛发声生器电路

- ・ 一款节能电路

- ・ 利用太阳能充电的旅行充电器

当前位置:

当前位置: