一种智能手机的低功率损耗设计

[09-14 01:03:46] 来源:http://www.88dzw.com 电子制作 阅读:8708次

文章摘要: 2.3.1 上拉电阻/下拉电阻的选取 软件优化是一个很重要的工作,可以大大提高软件运行时的效率和降低软件运行时的功耗。例如指令的重排,在不影响指令执行结果的情况下,可以消除由于装载延迟、分支延迟、跳转延迟等引起的指令流水线的失效[5]。如表1所示的arm汇编,把指令转变成二进制编码后,不同之处就是各个寄存器操作数的二进制编码不同。 根据表1,从电气性能上来看,通过减小连续指令之间的汉明(Hamming)距离,原代码比优化后代码的比特位变化多6次,而两组代码实现同样的功能,因此,优化后的指令执行时的功耗小于原先指令。因此,系统软件完成后,在保证软件功能一致的情况

一种智能手机的低功率损耗设计,标签:电子小制作,http://www.88dzw.com2.3.1 上拉电阻/下拉电阻的选取

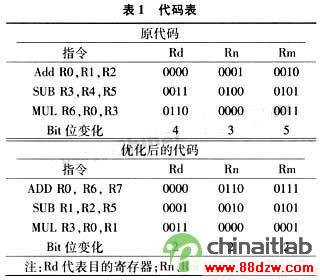

软件优化是一个很重要的工作,可以大大提高软件运行时的效率和降低软件运行时的功耗。例如指令的重排,在不影响指令执行结果的情况下,可以消除由于装载延迟、分支延迟、跳转延迟等引起的指令流水线的失效[5]。如表1所示的arm汇编,把指令转变成二进制编码后,不同之处就是各个寄存器操作数的二进制编码不同。

根据表1,从电气性能上来看,通过减小连续指令之间的汉明(Hamming)距离,原代码比优化后代码的比特位变化多6次,而两组代码实现同样的功能,因此,优化后的指令执行时的功耗小于原先指令。因此,系统软件完成后,在保证软件功能一致的情况下,通过对代码进行优化,可以减小软件在执行时的功耗。

3 试验结果和讨论

在智能手机的设计中,通过不断进行硬件优化和在软件上实现电源的动态管理,测量智能手机在空闲模式和睡眠模式下的功率损耗,结果如表2所示。

从表2可以看出,经过优化设计,智能手机在空闲模式下,电流值减小了10.2 mA,在睡眠模式下,电流值减少了1.5 mA。对于无线Modem,由于自身含有独立的电源管理模块,基本上在3 mA左右,变化不大。相比未经优化设计,智能手机经过优化设计后,在睡眠模式下和空闲模式下,功率损耗有了显著的降低,在相同的电池容量下,大大提高了智能手机的待机时间和使用时间。因此,通过上述方法,可以有效地降低智能手机的功耗。

随着手机技术的发展,特别在智能手机设计中,低功耗设计会成为一个越来越迫切的问题。随着一些新技术的出现并应用于智能手机的设计中,例如先进的电源管理芯片、先进的处理器,给设计者提供了更大的灵活性,可以大大降低智能手机功耗。但是,作为设计者,在进行系统设计和软件编程时,必须时时考虑如何降低系统的功耗,只有这样,设计出的系统才能拥有一个良好的性能,得到用户的青睐。

对于主CPU来说,内核供电电压为1.3 V,已经很小,而且其全速运行时的主频可以完全根据需要进行设置,其内部所需的其他各种频率都是通过主频分频产生。主CPU主频fCPU计算公式如下:

在COMS芯片上,为了防止静电造成损坏,不用的引脚不能悬空,一般接下拉电阻来降低输入阻抗,提供泄荷通路。需要加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限来增强抗干扰能力。但是在选择上拉电阻时,必须要考虑以下几点:

a)从节约功耗及芯片的倒灌电流能力上考虑,上拉电阻应足够大,以减小电流;

b)从确保足够的驱动电流考虑,上拉电阻应足够小,以增大电流;

c)在高速电路中,过大的上拉电阻会使信号边沿变得平缓,信号完整性会变差。

因此,在考虑能够正常驱动后级的情况下(即考虑芯片的VIH或VIL),尽可能选取更大的阻值,以节省系统的功耗。对于下拉电阻,情况类似。

2.3.2 对悬空引脚的处理

对于系统中CMOS器件的悬空引脚,必须给予重视。因为CMOS悬空的输入端的输入阻抗极高,很可能感应一些电荷导致器件被高压击穿,而且还会导致输入端信号电平随机变化,导致CPU在休眠时不断地被唤醒,从而无法进入睡眠状态或其他莫名其妙的故障。所以正确的方法是,根据引脚的初始状态,将未使用的输入端接到相应的供电电压来保持高电平,或通过接地来保持低电平。

- 上一篇:基于SoC的音频IP模块设计

《一种智能手机的低功率损耗设计》相关文章

- › 一种智能手机的低功率损耗设计

- 在百度中搜索相关文章:一种智能手机的低功率损耗设计

- 在谷歌中搜索相关文章:一种智能手机的低功率损耗设计

- 在soso中搜索相关文章:一种智能手机的低功率损耗设计

- 在搜狗中搜索相关文章:一种智能手机的低功率损耗设计

编辑推荐

- ・ 自制教室照明节电控制器

- ・ 双色音乐彩灯的制作

- ・ 三相交流电机缺相保护器

- ・ 声光控节能灯的制作

- ・ 同线电话转呼及互通器电路

- ・ 超低频信号发生器的制作

- ・ 自制热转印电路板

- ・ 警笛发声生器电路

- ・ 一款节能电路

- ・ 利用太阳能充电的旅行充电器

当前位置:

当前位置: