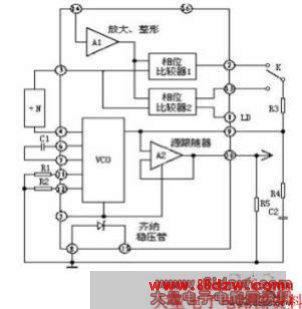

过零比较和相位比较电路原理图

[11-27 03:50:04] 来源:http://www.88dzw.com 基本电路电路图 阅读:8921次

文章摘要:现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。下图是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如图1所示。1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。2脚相位比较器Ⅰ的输出端。3脚比较信号输入端。13脚相位比较器Ⅱ的输出端。14脚信号输入端。对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。如果两信号的频率相同而相位不同,当输人信号的相位滞后于

过零比较和相位比较电路原理图,标签:电路图讲解,电路图练习,http://www.88dzw.com 现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。下图是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如图1所示。

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。2脚相位比较器Ⅰ的输出端。3脚比较信号输入端。13脚相位比较器Ⅱ的输出端。14脚信号输入端。对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。上述波形如图2.13所示。由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了。

电路图 src="/pd_dianzi/UploadPic/2010-11/2010112115013688.jpg" border=0 style="cursor:pointer;" onload="return imgzoom(this,600);" onclick="javascript:window.open(this.src);" style="cursor:pointer;"/>

图2 比较器输出波形图

Tag:基本电路电路图,电路图讲解,电路图练习,电子电路图 - 基本电路电路图

《过零比较和相位比较电路原理图》相关文章

- › 过零比较和相位比较电路原理图

- 在百度中搜索相关文章:过零比较和相位比较电路原理图

- 在谷歌中搜索相关文章:过零比较和相位比较电路原理图

- 在soso中搜索相关文章:过零比较和相位比较电路原理图

- 在搜狗中搜索相关文章:过零比较和相位比较电路原理图

编辑推荐

- ・ 晶体管双稳态触发电路

- ・ 可控硅驱动放大电路

- ・ KJ001的典型应用电路图

- ・ 调制器电路图

- ・ 由可控硅过零触发器KJ009组成的应用电路图

- ・ 固体继电器SSR

分类导航

最新更新

- ・ 试验信号发生器用调制器电路图

- ・ 阻抗式湿敏元件应用电路图

- ・ 基于恒定输出阻抗电路图

- ・ LS7232组成的触摸调光灯电路图

- ・ 落料自动调节装置电路图

- ・ 调光台灯电路图

- ・ 阻抗变换器电路图

- ・ 调制器电路之低频电路图

- ・ 调制器电路图

- ・ 直流调压电路图

热门排行

当前位置:

当前位置: