ʵ��ģ2��������·

[09-12 12:17:32] ��Դ��http://www.88dzw.com ��·���� �Ķ���8751��

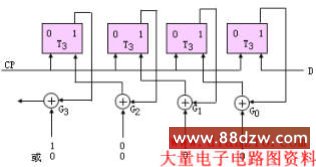

����ժҪ��ʵ��ģ2��������·ѭ��У����ĺ�������·��ʵ��ģ2������·������ǰ����ܵķ������ɽ�ģ2���IJ���ֽ����Ϊ���ֲ�������������������������λ��ֵΪ0��ֱ�ӽ���������һλ��������������������λ��ֵΪ1�������ɶ���ʽG(x)��ģ2����Ȼ����������һλ��ͼ2.2 ʵ��ģ2������ͼ ��ǰ����G(x)=1011����(7,4)У��������ӣ��ɲ���ͼ2.2��ʾ��·������3λ��������ͼ�е�ģ2���������ʵ�֣�����һλ����λ�Ĵ���ʵ�֣�������ŵ�����������һλ�Ĵ�����D����ˣ���ͬʱʵ��ģ2�������ơ�������һλ��ȡֵ�����Ƿ���ģ2��������Ϊ1ʱ����ȥ�����������ɶ���ʽG(x)=1011�����������

ʵ��ģ2��������·,��ǩ�����ӵ�·����,ģ���·����,http://www.88dzw.comʵ��ģ2��������·

����ѭ��У����ĺ�������·��ʵ��ģ2������·������ǰ����ܵķ������ɽ�ģ2���IJ���ֽ����Ϊ���ֲ�������������������������λ��ֵΪ0��ֱ�ӽ���������һλ��������������������λ��ֵΪ1�������ɶ���ʽG(x)��ģ2����Ȼ����������һλ��

ͼ2.2 ʵ��ģ2������ͼ

������ǰ����G(x)=1011����(7,4)У��������ӣ��ɲ���ͼ2.2��ʾ��·������3λ��������ͼ�е�ģ2���������ʵ�֣�����һλ����λ�Ĵ���ʵ�֣�������ŵ�����������һλ�Ĵ�����D����ˣ���ͬʱʵ��ģ2�������ơ�������һλ��ȡֵ�����Ƿ���ģ2��������Ϊ1ʱ����ȥ�����������ɶ���ʽG(x)=1011�����������D����λ�����͵���λ�Ĵ����ģ�����CP����ͬ����

ͼ2.3 ʵ��G(x)=1011������(7,4)������ģ2����·ͼ

��������G(x)�̶����䣬��G2��ʡȥ��ֻ����λ��������G3��T0Ҳʧȥ���塣ͼ2.2�ɼ�Ϊͼ2.3(a)��

��ͼ2.3(a)����·��˵���ڷ��Ͷˣ�������Ϣ��DΪ1100�����дӵ�λ���룬��������λ�γ�1100000����ͨ��7��ģ2����������λ�Ĵ��� T3 T2 T1 �еõ�����010���ڽ��նˣ���7λ��CRC����1100010��ִ��7��ģ2��֮������ T3 T2 T1 �õ�000������CRC���������κ�һλ��������������Ϊȫ0���ɸ��ݱ�2.4ȷ������λ�á�

������TiΪT3T2T1ij��������ǰ״̬��Ti'Ϊ��̬�����ô�̬���̱�ʾͼ2.3(a)��ģ2����·�� T3'=T2, T2'=T3��T1 , T1'=T3��D��

�ֱ��ñ�����1100000��1010000��֤ȡ������Ϊ010��011�Ĺ������̣�����2.6�����߿���ģ2����ʽ��������������֮�Ƚϡ�

| ���� | ��Ϣ��1100 | ��Ϣ��1010 |

| ����D TTT | ����D TTT | |

|

��̬ 1 2 3 4 5 6 7 |

��0 ��000 ��1 ��001 ��1 ��011 ��0 ��110 ��0 ��111 ��0 ��101 ��0 ��001 ��0 ��010 |

��0 ��000 ��1 ��001 ��0 ��010 ��1 ��101 ��0 ��001 ��0 ��010 ��0 ��100 ��0 ��011 |

�������Խ�ͼ2.3(a)����·�Լӱ仯�����õ�ͼ2.3(b)����·������ΪG(x)=1011��ϵͳ����(7,4)������ı�����·����������ϢD�ɸ�λ�����룬CRC����T�ͳ�����ʼʱ������K1�պϣ�K2��bλ�ã�������Ϣ���������·��ͬʱ�͵�T���������4��֮��,T3T2T1��Ϊ������Ȼ��K1�Ͽ���K2��a��T3T2T1ֻ����λ���ܣ����ý�����ƴ������Ϣ���T�ͳ���ͼ2.3(b)�У�����K

Tag:��·���������ӵ�·����,ģ���·��������·����

- ��һƪ�������ݵı�ʾ

��ʵ��ģ2��������·���������

- › ʵ��ģ2��������·

- �ڰٶ�������������£�ʵ��ģ2��������·

- �ڹȸ�������������£�ʵ��ģ2��������·

- ��soso������������£�ʵ��ģ2��������·

- ���ѹ�������������£�ʵ��ģ2��������·

�༭�Ƽ�

���ർ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

���¸���

- �� ʲô��ϵͳ����

- �� ʲô��CPCI

- �� Ӣ�ض� Parallel Composer����

- �� ʲô��֧�����ݿ�,ʲô���к����ݿ�

- �� ʲô�����ݽ�������

- �� ʲô���ڲ����ݴ�����

- �� ʲô�ǿռ����ݽ�������

- �� ʲô�Dz��챸��

- �� ʲô�DZ��ݼ�

- �� ʲô��ӳ��

��������

��ǰλ�ã�

��ǰλ�ã�