如何减少传输线效应

[08-09 21:17:10] 来源:http://www.88dzw.com 布线技巧与EMC 阅读:8594次

文章摘要:2、合理规划走线的拓扑结构解决传输线效应的另一个方法是选择正确的布线路径和终端拓扑结构。当使用高速逻辑器件时,除非走线分支长度保持很短,否则边沿快速变化的信号将被信号主干走线上的分支走线所扭曲。通常情形下,PCB走线采用两种基本拓扑结构,即菊花链(Daisy Chain)布线和星形(Star)分布。对于菊花链布线,布线从驱动端开始,依次到达各接收端。如果使用串联电阻来改变信号特性,串联电阻的位置应该紧靠驱动端。在控制走线的高次谐波干扰方面,菊花链走线效果最好。但这种走线方式布通率最低,不容易100%布通。实际设计中,我们是使菊花链布线中分支长度尽可能短,安全的长度值应该是:Stub Delay

如何减少传输线效应,标签:布线,emc是什么意思,http://www.88dzw.com

2、合理规划走线的拓扑结构

解决传输线效应的另一个方法是选择正确的布线路径和终端拓扑结构。当使用高速逻辑器件时,除非走线分支长度保持很短,否则边沿快速变化的信号将被信号主干走线上的分支走线所扭曲。通常情形下,PCB走线采用两种基本拓扑结构,即菊花链(Daisy Chain)布线和星形(Star)分布。

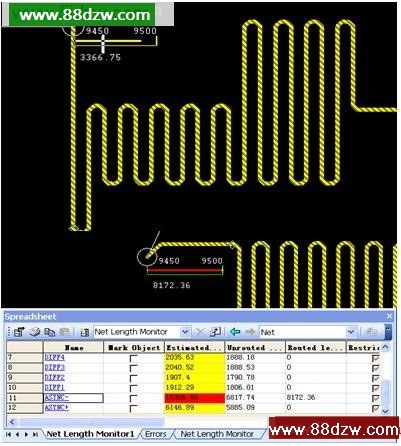

对于菊花链布线,布线从驱动端开始,依次到达各接收端。如果使用串联电阻来改变信号特性,串联电阻的位置应该紧靠驱动端。在控制走线的高次谐波干扰方面,菊花链走线效果最好。但这种走线方式布通率最低,不容易100%布通。实际设计中,我们是使菊花链布线中分支长度尽可能短,安全的长度值应该是:Stub Delay <= Trt *0.1

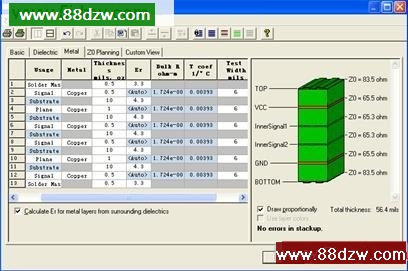

星形拓扑结构可以有效的避免时钟信号的不同步问题,但在密度很高的PCB板上手工完成布线十分困难。采用自动布线器是完成星型布线的最好的方法。每条分支上都需要终端电阻。终端电阻的阻值应和连线的特征阻抗相匹配。这可通过软件仿真计算,得到特征阻抗值和终端匹配电阻值。

3、抑止电磁干扰的方法

很好地解决信号完整性问题将改善PCB板的电磁兼容性(EMC)。其中非常重要的是保证PCB板有很好的接地。对复杂的设计采用一个信号层配一个地线层是十分有效的方法。此外,使电路板的最外层信号的密度最小也是减少电磁辐射的好方法,这种方法可采用"表面积层"技术"Build-up"设计做PCB来实现。表面积层通过在普通工艺 PCB 上增加薄绝缘层和用于贯穿这些层的微孔的组合来实现 ,电阻和电容可埋在表层下,单位面积上的走线密度会增加近一倍,因而可降低 PCB的体积。PCB 面积的缩小对走线的拓扑结构有巨大的影响,这意味着缩小的电流回路,缩小的分支走线长度,而电磁辐射近似正比于电流回路的面积;同时小体积特征意味着高密度引脚封装器件可以被使用,这又使得连线长度下降,从而电流回路减小,提高电磁兼容特性。

4、其它可采用技术

为减小集成电路芯片电源上的电压瞬时过冲,应该为集成电路芯片添加去耦电容。这可以有效去除电源上的毛刺的影响并减少在印制板上的电源环路的辐射。

当去耦电容直接连接在集成电路的电源管腿上而不是连接在电源层上时,其平滑毛刺的效果最好。这就是为什么有一些器件插座上带有去耦电容,而有的器件要求去耦电容距器件的距离要足够的小。

任何高速和高功耗的器件应尽量放置在一起以减少电源电压瞬时过冲。

如果没有电源层,那么长的电源连线会在信号和回路间形成环路,成为辐射源和易感应电路。

走线构成一个不穿过同一网线或其它走线的环路的情况称为开环。如果环路穿过同一网线其它走线则构成闭环。两种情况都会形成天线效应(线天线和环形天线)。天线对外产生EMI辐射,同时自身也是敏感电路。闭环是一个必须考虑的问题,因为它产生的辐射与闭环面积近似成正比。

最后一个问题,上文所述的经验方法,在实际操作过程中人工计算是无法完成的,需要通过软件仿真和EDA软件控制。

针对传输线问题所引入的影响,本文严格控制关键网线的走线长度等四个方面总结了控制这些影响的方法。这些方法都是在实践中总结出来的,也希望对读者朋友们有所帮助。

- 上一篇:通孔插装PCB板的设计分析

当前位置:

当前位置: