PCI总线系统体系结构

[09-13 16:55:07] 来源:http://www.88dzw.com 接口定义 阅读:8271次

文章摘要:作者:杨硕,www.88dzw.com嵌入式学院讲师。PCI (Peripheral Component Interconnect)总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。在数字图形、图像和语音处理,以及高速实时数据采集与处理等对数据传输率要求较高的应用中,采用PCI总线来进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。PCI是目前计算机插卡式外设总线的事实标准。PCI提供了一组完整的总线接口规范,其目的是描述如何将计算机系统中的外围设备以一种结构化和可控化的方式连接在一起,同时它还刻画了外围设备在连接时的电气特性和行为规约,并且详细定

PCI总线系统体系结构,标签:接口技术,微机原理与接口技术,http://www.88dzw.com作者:杨硕,www.88dzw.com嵌入式学院讲师。

PCI (Peripheral Component Interconnect)总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。在数字图形、图像和语音处理,以及高速实时数据采集与处理等对数据传输率要求较高的应用中,采用PCI总线来进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。PCI是目前计算机插卡式外设总线的事实标准。

PCI提供了一组完整的总线接口规范,其目的是描述如何将计算机系统中的外围设备以一种结构化和可控化的方式连接在一起,同时它还刻画了外围设备在连接时的电气特性和行为规约,并且详细定义了计算机系统中的各个不同部件之间应该如何正确地进行交互。

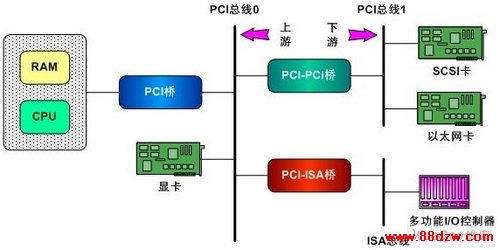

同旧式的ISA总线不同,PCI将计算机系统中的总线子系统与存储子系统完全地分开,CPU通过一块称为PCI桥(PCI-Bridge)的设备来完成同总线子系统的交互,如下图所示:

由于使用了更高的时钟频率,因此PCI总线能够获得比ISA总线更好的整体性能。PCI总线的时钟频率一般在25MHz到33MHz范围内,有些甚至能够达到66MHz或者133MHz,而在64位系统中则最高能达到266MHz。尽管目前PCI设备大多采用32位数据总线,但PCI规范中已经给出了64位的扩展实现,从而使PCI总线能够更好地实现平台无关性,现在PCI总线已经能够用于IA-32、Alpha、PowerPC、SPARC64和IA-64等体系结构中。

PCI总线具有五个非常显著的优点,使得它能够完成最终取代ISA总线这一历史使命:

● PCI总线的地址总线与数据总线是分时复用的,

● 在计算机和外设间传输数据时具有更好的性能;

● 能够尽量独立于具体的平台;

● 可以很方便地实现即插即用;

● 中断共享的实现

下图是一个典型的基于PCI总线的计算机系统逻辑示意图,系统的各个部分通过PCI总线和PCI-PCI桥连接在一起。从图中不难看出,CPU和RAM需要通过PCI桥连接到PCI总线0(即主PCI总线),而具有PCI接口的显卡则可以直接连接到主PCI总线上。PCI-PCI桥是一个特殊的PCI设备,它负责将PCI总线0和PCI总线1(即从PCI主线)连接在一起,通常PCI总线1称为PCI-PCI桥的下游(downstream),而PCI总线0则称为PCI-PCI桥的上游(upstream)。图中连接到从PCI总线上的是SCSI卡和以太网卡。为了兼容旧的ISA总线标准,PCI总线还可以通过PCI-ISA桥来连接ISA总线,从而能够支持以前的ISA设备。图中ISA总线上连接着一个多功能I/O控制器,用于控制键盘、鼠标和软驱。

PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定在谁有权力拿到总线的主控权。在PCI应用系统中,如果一个设备取得了总线控制权,就称之为“主设备”,而被主设备选中以进行通信的设备称为“从设备”或“目标设备”。

在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。

“本文由www.88dzw.com提供”

《PCI总线系统体系结构》相关文章

- › 基于PCI总线的实时测频卡WDM驱动程序设计

- › 基于CPCI总线的多网口卡设计

- › PCI总线I/O时序波形观测及分析

- › PCI总线系统体系结构

- › 基于PCI总线芯片CH365的数据密码卡设计

- › 基于FPGA的PCI总线接口硬件调试策略

- 在百度中搜索相关文章:PCI总线系统体系结构

- 在谷歌中搜索相关文章:PCI总线系统体系结构

- 在soso中搜索相关文章:PCI总线系统体系结构

- 在搜狗中搜索相关文章:PCI总线系统体系结构

当前位置:

当前位置: