元器件堆叠封装与组装的结构

[09-12 18:50:24] 来源:http://www.88dzw.com PCB设计 阅读:8391次

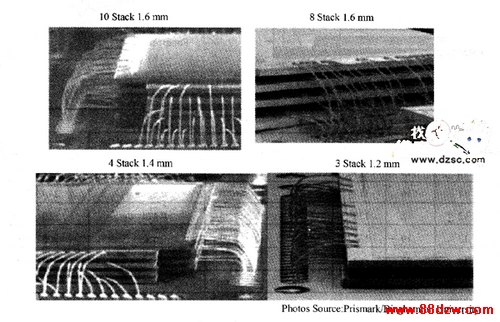

文章摘要:元器件内芯片的堆叠大部分是采用金线键合的方式(Wire Bonding),堆叠层数可以从2~8层)。 STMICRO声称,诲今厚度到40μm的芯片可以从2个堆叠到8个(SRAM,Hash和DRAM),40μm的芯片堆叠8个总 厚度为1.6 mm,堆叠两个厚度为0.8 mm。如图1所示。图1 元器件内芯片的堆叠堆叠元器件(Amkor PoP)典型结构如图2所示:・底部PSvfBGA(Package Stackable very thin fine pitch BGA);・顶部Stacked CSP(FBGA, Fine pitch BGA)。图2 堆叠元器件实行结构图1. 底部 PSvfBGA(

元器件堆叠封装与组装的结构,标签:pcb培训,pcb是什么,pcb软件,http://www.88dzw.com元器件内芯片的堆叠大部分是采用金线键合的方式(Wire Bonding),堆叠层数可以从2~8层)。 STMICRO声称,诲今厚度到40μm的芯片可以从2个堆叠到8个(SRAM,Hash和DRAM),40μm的芯片堆叠8个总 厚度为1.6 mm,堆叠两个厚度为0.8 mm。如图1所示。

图1 元器件内芯片的堆叠

堆叠元器件(Amkor PoP)典型结构如图2所示:

・底部PSvfBGA(Package Stackable very thin fine pitch BGA);

・顶部Stacked CSP(FBGA, Fine pitch BGA)。

图2 堆叠元器件实行结构图

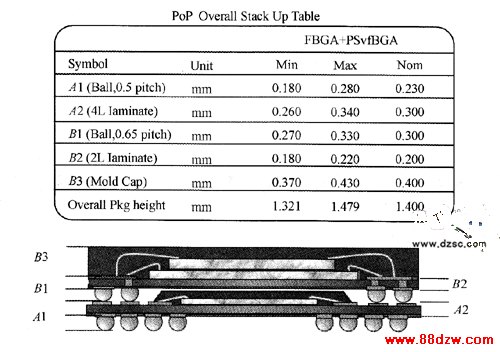

1. 底部 PSvfBGA(Package stackab丨e very thin fine pitch BGA)结构(如图3所示)

・外形尺寸:10~15 mm;

・中间焊盘间距:0.65 mm,底部焊球间距:0.5 mm(0.4mm);

・基板:FR-5;

・焊球材料:63Sn37Pb/Pb-free。

图3 底部PSvfBGA结构

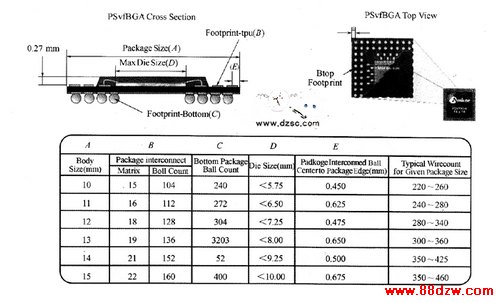

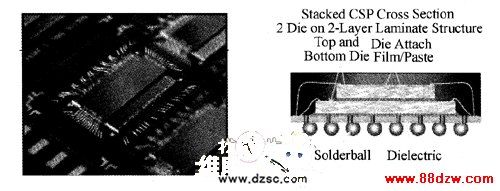

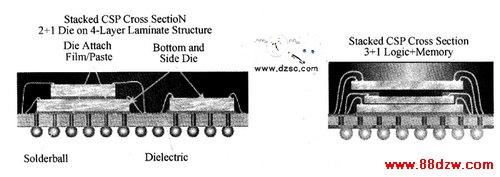

2.顶部scsP结构(如图4和图5所示)

・外形尺寸:4~21 mm;

・底部球间距:0.4~0.8 mm;

・ 基板: Polyimide;

・焊球材料:63 Sn37Pb/Pb-free;

・球径:0.25~0.46 mm。

图4 顶部scsP结构图(1)

图5 顶部SCSP结构图(2)

3.底部元件和顶部元件组装后的空间关系(如图6所示)

PoP装配的重点是需要控制元器件之间的空间关系。如果它们之间没有适当的间隙,那么就会有应力的存在 ,而这对于可靠性和装配良率来讲是致命的影响。PoP组装后的空间关系如图6所示。概括起来,其空间关系 有以下几点需要我们关注:

・底部器件的模塑高度(0.27~0.35 mm);

・顶部器件回流前焊球的高度与间距e1;

・回流前,顶部器件底面和底部元件顶面的间隙fl;

・顶部器件回流后焊球的高度与间距e2;

・回流后,顶部器件底面和底部元件顶面的间隙f2。

图6 PoP组装后空间关系

而影响其空间关系的因素除了基板和元器件设计方面,还有基板制造工艺、元件封装工艺以及SMT装配工艺,以下是都需要加以关注的方面:

・焊盘的设计;

・阻焊膜窗口尺寸及位置公差;

・焊球尺寸公差;

・焊球高度差异;

・蘸取的助焊剂或锡膏的量:

・贴装的精度:

・回流环境和温度;

・元器件和基板的翘曲变形:

・底部器件模塑厚度。

欢迎转载,信息来源www.88dzw.com(www.88dzw.com)

- 上一篇:多功能贴片机的结构特点

《元器件堆叠封装与组装的结构》相关文章

- › 元器件堆叠封装与组装的结构

- 在百度中搜索相关文章:元器件堆叠封装与组装的结构

- 在谷歌中搜索相关文章:元器件堆叠封装与组装的结构

- 在soso中搜索相关文章:元器件堆叠封装与组装的结构

- 在搜狗中搜索相关文章:元器件堆叠封装与组装的结构

当前位置:

当前位置: