����cyclone EP1C6 ��LED������Ʒ���

[09-13 16:47:02] ��Դ��http://www.88dzw.com ��Ϣ��ʾ���缼�� �Ķ���8222��

����ժҪ�� ժ Ҫ��������һ�ֻ���FPGA��LED������Ʒ����������Զ����µ����˼�룬����˻���FPGA��˫��RAM��ɨ����Ƶ�·������˴�ͳLED��������У�����ϵͳ���өp�ɿ��Բ�����⡣ �ؼ��ʣ���Ƭ����FPGA�� LED����Ļ,˫��RAM Ŀǰ���õ�LED����Ļ��ʾϵͳ�Ŀ��Ƶ�·������ɵ�������CPU�����ӵ���Χ��·��ɣ����ֵ�·��ƣ���Ƭ����̱Ƚϸ��ӣ�������·�ĵ��ԱȽ��鷳���ɿ��Ժ�ʵʱ�Ժ��ѵõ���֤������������������һ�ֻ���cyclone EP1C6��LED����Ļ��Ʒ���,����Ʒ����������FLASH ROM��RAM�������κ��ⲿ���ܵ�·�����й��ܾ���һƬcyclon

����cyclone EP1C6 ��LED������Ʒ���,��ǩ����ʾ�����,�����ʾ����,http://www.88dzw.com ժ Ҫ��������һ�ֻ���FPGA��LED������Ʒ����������Զ����µ����˼�룬����˻���FPGA��˫��RAM��ɨ����Ƶ�·������˴�ͳLED��������У�����ϵͳ���өp�ɿ��Բ�����⡣

�ؼ��ʣ���Ƭ����FPGA�� LED����Ļ,˫��RAM

Ŀǰ���õ�LED����Ļ��ʾϵͳ�Ŀ��Ƶ�·������ɵ�������CPU�����ӵ���Χ��·��ɣ����ֵ�·��ƣ���Ƭ����̱Ƚϸ��ӣ�������·�ĵ��ԱȽ��鷳���ɿ��Ժ�ʵʱ�Ժ��ѵõ���֤������������������һ�ֻ���cyclone EP1C6��LED����Ļ��Ʒ���,����Ʒ����������FLASH ROM��RAM�������κ��ⲿ���ܵ�·�����й��ܾ���һƬcyclone EP1C6��һƬ��Ƭ��SPCE061A��ʵ�֣��������ݴ����ٶȿ졢�ɿ��Ըߵ��ص㡣����FPGA�ڲ�˫��RAM�����ã�Ϊ��ͬ���������ͨ���ṩ��һ���µĽ����������

1 ϵͳ�ṹ�����ܸ���

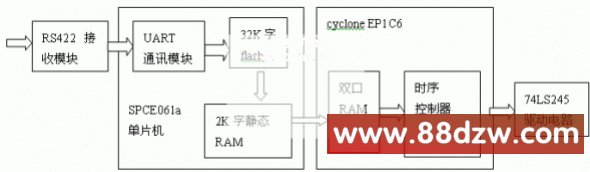

��ƶ�����һ�����192��128����ɫLED����ĵ������������������ģ�黯�Ľṹ��ÿ4��16��16�ĵ����Ϊһ����Ԫ����3��8�������ĵ�Ԫ������Ҫ��������ʾ5�����ݣ���ÿ���������������ƶ��ȶ���Ч����ʵ��Ӧ�����������Ҿ��������ԼΪ200�ס������ƶ����Ҫ��ʹ���Ļ��Ƶ��ص㣬ϵͳ�ṹ��ͼ��ͼ1��ʾ��

ͼ1 ϵͳ��ͼ

LED�������ϵͳ��������Ҫ��Ԫ��ɣ���λ��ͼ��/���ֱ༭�뷢�Ͳ��ֵ�Ԫ�����ذ嵥Ԫ��LED��������ϵͳ��λ����һ̨PC�������ƣ���Ҫ�DZ༭������ͼ��/������Ϣ�����ذ壬�����ذ����Щ���ݽ��д������͵�����Ļ����ʾ������

2 ϵͳӲ�����

ϵͳӲ�������Ҫ�Ƕ����ذ����ƣ����ذ����Ҫ���ܰ���������ͨѶ�����ݴ洢�����ݴ�����ɨ����Ƶȡ���ͳLED�����������Ϊ���ݴ洢����FLASH ROM�����ݴ�����������RAM��CPU�Ϳɱ��������FPGA/CPLD����Ϊ����ɨ�軺������RAM��ɣ���ṹ��ͼ2��ʾ��

ͼ2 ��ͳLED����������ذ�ṹͼ

��ͳ���ذ�Ӳ�������Ҫ�϶����Χ�������е�����л���ֹһ��CPU��CPLD��������Ӳ���ṹ�����߸��ӣ�������Ƴɱ��ϸߡ����⣬����LED����Ļ�������ܴ��������洢��֮�䡢��Ƭ����FPGA/CPLD֮ǰ����ʵʱ�ɿ��Ĵ���Ҳ��һ�����⡣Ϊ�����Щ���⣬���ذ�Ӳ����·�����ѡ��һƬ������Ƭ��SPCE061A��һƬFPGA cyclone EP1C6����ṹ��ͼ��ͼ3��ʾ��

ͼ3 ����cyclone EP1C6�����ذ�ṹͼ

2.1 cyclone EP1C6��SPCE061A���

cyclone EP1C6��Altera�Ƴ���һ����Լ۱�FPGA��������ѹ3.3V���ں˵�ѹ1.5V������0.13��m���ռ�����ȫͭSRAM���գ����ܶ�Ϊ5980������Ԫ������20��128��36λ��RAM�飨M4Kģ�飩���ܵ�RAM�ռ�ﵽ92160λ����Ƕ2�������·��һ����������SDRAM���ض�˫�����ʽӿڣ�����Ƶ�ʸߴ�200MHz

- ��һƪ����α��LCD��ʾ���Ļ��������

������cyclone EP1C6 ��LED������Ʒ������������

- › ����CY7C68013A��USB����ϵͳ����о�

- › ����cyclone EP1C6 ��LED������Ʒ���

- › ����CYGNAL��Ƭ����FPGA����̨���˿����������

- �ڰٶ�������������£�����cyclone EP1C6 ��LED������Ʒ���

- �ڹȸ�������������£�����cyclone EP1C6 ��LED������Ʒ���

- ��soso������������£�����cyclone EP1C6 ��LED������Ʒ���

- ���ѹ�������������£�����cyclone EP1C6 ��LED������Ʒ���

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- �� Avago �Ƴ�������ů��ɫ����ʽLED��Ʒ

- �� ��ɭ�� �Ƴ���С����·���LED������

- �� Avago �³�������Extra Bright IIϵ��LED

- �� Avago �Ƴ�1Wů��ɫ��LED��Ʒ

- �� TI �Ƴ�1.2A�����������LED������

- �� Linear �Ƴ�250mAͨ�÷��ѵ绰LED������

- �� Holtek �Ƴ��ߵ���LED����I/O��������

- �� Maxim�Ƴ���LED (WLED)������MAX8901A/B

- �� ����Ƕ��ʽLinux��TFT LCD IP�����������

- �� HY-240128M-201ͼ�ε���ʽҺ����ʾģ�鼰��

- �� LED�����������������

- �� ����LEDƵ����Դ��������

- �� ����ĻLED������ʾϵͳ

- �� LED��Ļ��Ƽ���չ���ƣ�LED��Ļ����ϵͳ��

- �� Maxim�Ƴ���LED (WLED)������MAX8901A/B

- �� LCoS(���Һ��)��ʾ�������Ӧ��

- �� �����Ͷ˿���չ������LED

- �� NSMȫ��LED��������ϵͳ���ӶȲ�����ϵͳ

- �� DS90CF364LVDS����/��������RGBҺ����Ӧ��

- �� Ӱ�������LED�����������������

��ǰλ�ã�

��ǰλ�ã�