低压CM0S带隙基准电压源设计

[10-10 20:39:48] 来源:http://www.88dzw.com 电源电路 阅读:8684次

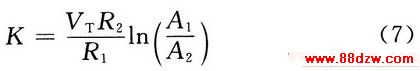

文章摘要:式中;A1和A2是Q1和Q2的发射极面积。比较式(5)和式(1),可得常数K为: 在实际设计中,K值即为式(7)表示。 传统带隙基准源结构能输出比较精确的电压,但其电源电压较高(大于3 V),且基准输出范围有限(1.2 V以上)。要在1.8 V以下的电源电压得到1.2 V以下的精确基准电压,就必须对基准源结构上进行改进和提高。1.2 低压COMS基准电压源的电路设计 本设计基于CSMC-O.5μm-CMOS工艺(NMOS的阈值电压为0.536 V,PMOS的阈值电压为-0.736 V)。采用一级温度补偿、电流反馈技术设计的低压带隙基准源电路如图3所示。低压带隙基准源

低压CM0S带隙基准电压源设计,标签:电源电路,电路设计,http://www.88dzw.com式中;A1和A2是Q1和Q2的发射极面积。比较式(5)和式(1),可得常数K为:

在实际设计中,K值即为式(7)表示。

传统带隙基准源结构能输出比较精确的电压,但其电源电压较高(大于3 V),且基准输出范围有限(1.2 V以上)。要在1.8 V以下的电源电压得到1.2 V以下的精确基准电压,就必须对基准源结构上进行改进和提高。

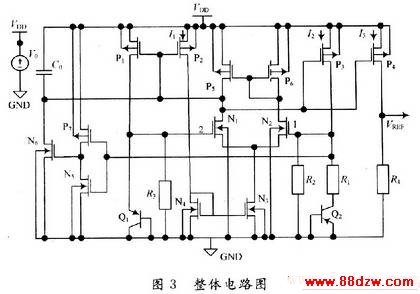

1.2 低压COMS基准电压源的电路设计

本设计基于CSMC-O.5μm-CMOS工艺(NMOS的阈值电压为0.536 V,PMOS的阈值电压为-0.736 V)。采用一级温度补偿、电流反馈技术设计的低压带隙基准源电路如图3所示。低压带隙基准源的电流不仅用于提供基准输出所需的电流,也用于产生差分放大器所需的电流源偏置电压,简化了电路和版图设计。

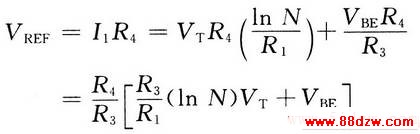

输出电压VREF为:

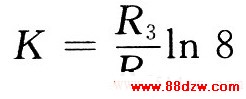

电路中的温度补偿系数K为:

通过调节R4的值,可以调节输出电压VREF的大小。在电源电压变化时,P2,P3,P4的漏源电压值保持不变,与电源电压无关,其栅极电压由运放调节。为了降低电路的复杂度,应用电流反馈原理,运放采用简单的一阶运放,由于VDD的变化多于GND的变化,故运放的输入采用NMOS的差分对结构。因为整个电路在低压下工作,故整个电路设计的重点是要保证低压下运放的正常工作。

由于带隙基准源存在两个电路平衡点,即零点和正常工作点。当基准源工作在零点时,节点1、2的电压等于零,基准源没有电流产生。固需要设计一个启动电路,避免基准源工作在平衡零点。本设计的启动电路由N5、N6和P7构成。当电路工作在零点时,N6管导通,迅速提高节点1、2的电压,产生基准电流,节点1的电压通过P7和N5组成的反相器,使N6管完全截止,节点1、2的电压回落在稳定的工作点上,基准源开始正常工作。

电路的器件参数如表1所示,P2,P3,P4管的尺寸较大,是为了降低电路中的1/f噪声。电流镜的负载管P5,P6和差分对管N1,N2的宽长比较大,以抑制电路的热噪声。由于电路中的电阻值较大,故在工艺中用阱电阻实现。电容C0有助于电路的稳定,同时还可以减小于运放的宽度,有助于降低噪声的影响。

Tag:电源电路,电源电路,电路设计,家电维修 - 单元电路介绍 - 电源电路

《低压CM0S带隙基准电压源设计》相关文章

- › 低压CM0S带隙基准电压源设计

- 在百度中搜索相关文章:低压CM0S带隙基准电压源设计

- 在谷歌中搜索相关文章:低压CM0S带隙基准电压源设计

- 在soso中搜索相关文章:低压CM0S带隙基准电压源设计

- 在搜狗中搜索相关文章:低压CM0S带隙基准电压源设计

最新更新

当前位置:

当前位置: