FIR数字滤波器的FPGA实现研究

[09-14 00:27:49] 来源:http://www.88dzw.com 通信电路 阅读:8297次

文章摘要: 上世纪70年代Croisie提出了分布式算法DA(Distributed Arithmetic),但由于其特别适合用FPGA实现,所以直到Xilinx公司在FPGA中使用查找表(LUT)后,DA才被广泛应用在FPGA求乘积和中。 FIR的滤波输出y可以表示为输入x和系数h的内积: 由上述推导可知,分布式算法是一种以实现乘加运算为目的的运算方法。它与传统实现乘加运算的先后顺序不同。分布式算法在完成乘加功能时,是通过将各输入数据每一对应位产生的部分积预先进行相加形成相应部分积,然后在对各部分积预先进行累加形成最终结果;而传统算法是等到所有乘积产生之后再进行相加来完成乘加

FIR数字滤波器的FPGA实现研究,标签:电路设计,http://www.88dzw.com上世纪70年代Croisie提出了分布式算法DA(Distributed Arithmetic),但由于其特别适合用FPGA实现,所以直到Xilinx公司在FPGA中使用查找表(LUT)后,DA才被广泛应用在FPGA求乘积和中。

FIR的滤波输出y可以表示为输入x和系数h的内积:

由上述推导可知,分布式算法是一种以实现乘加运算为目的的运算方法。它与传统实现乘加运算的先后顺序不同。分布式算法在完成乘加功能时,是通过将各输入数据每一对应位产生的部分积预先进行相加形成相应部分积,然后在对各部分积预先进行累加形成最终结果;而传统算法是等到所有乘积产生之后再进行相加来完成乘加运算。

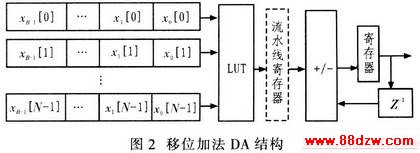

2.2 分布式FIR的实现结构

图2为分布式FIR滤波器的直接实现结构。对于小位宽的数据,DA算法不仅速度快,而且所占用的芯片资源少。

2.3 性能优化方法

1)流水线结构法 在滤波器中间增加适当的寄存器,构成流水线结构。在并行结构实现中添加流水线结构,可以提高滤波器速度,使其工作在更高的工作频率。对于速度固定的数据,可以通过多次复用乘累加器来节省资源。

2)查找表分隔法 在用LUT实现分布式算法时,由于LUT的规模随着N的增加呈现指数增长,如果滤波器系数N过大,则查找表的规模十分庞大。为了减小规模,可以利用部分表计算。由于FIR滤波器是线性滤波器,因此低阶滤波器输出可以相加,由此定义一个高阶滤波器的输出。例如,把16输入的查找表分割成4个并行的查找表。

查找表的分隔技术和流水线技术可以大大减小设计规模,同时并不会降低滤波速度。使用DA算法实现的FlR滤波器与传统的算法相比,DA算法可以极大地减少硬件电路规模,很容易实现流水线处理,提高电路的执行速度。

2.4 3种结构实现的比较

改进串行结构、并行结构、DA结构实现的比较如下:

1)改进串行结构 ①优点:使用资源少,只需一些寄存器、乘累加器便可完成整个滤波运算;②缺点:滤波速度慢,一次滤波所需的时钟数由滤波器的阶数决定。阶数较高的滤波器,滤波周期很大,无法实现高速滤波。

2)并行结构 ①优点:完成滤波的速度快,直接并行滤波器可以在一个时钟周期内完成一次滤波;②缺点:消耗大量的乘累加器,器件延迟较大,工作频率不可能太高。

3)DA结构 与串行结构实现相比,DA实现滤波速度较快,其滤波周期由数据宽度决定而与滤波器的阶数无关;而与并行实现相比,DA实现消耗的资源较少。且容易实现流水线处理,提高电路的执行速度。

在设计中,当资源成本为主要制约时,根据速度要求,选择串行结构实现或DA结构实现;而当速度成为主要制约时,则根据资源成本因素,选择并行实现结构或DA结构实现。在一般的应用设计中,一般采用DA结构实现。

3 实例设计与仿真

3.1 FIR滤波器的设计

利用Matlab中的FDATool工具设计一个33阶,Fs=48kHz,Fc=10.8 kHz的FIR滤波器,其幅值、相位响应见图3。为了便于FIR滤波器的FPGA实现,减小误差,将滤波器的系数量化取整后,在FPGA中实现采用的滤波系数为{-11,14,18,-11,-25,4,32,6,-38,-21,43,45,-47,-96,50,319,457,319,50,-96,-47,45,43,-21,-38,6,32,4,-25,-11,18,14,-11}。

Tag:通信电路,电路设计,家电维修 - 单元电路介绍 - 通信电路

《FIR数字滤波器的FPGA实现研究》相关文章

- › FIR数字滤波器的FPGA实现研究

- 在百度中搜索相关文章:FIR数字滤波器的FPGA实现研究

- 在谷歌中搜索相关文章:FIR数字滤波器的FPGA实现研究

- 在soso中搜索相关文章:FIR数字滤波器的FPGA实现研究

- 在搜狗中搜索相关文章:FIR数字滤波器的FPGA实现研究

最新更新

当前位置:

当前位置: