实用模拟BIST的基本原则

[10-10 20:38:44] 来源:http://www.88dzw.com 其它电路 阅读:8852次

文章摘要:3 基础电路原则3.1 原则一通过施加时序不敏感的数字测试模式、时钟以及DC电压,测试机制本身必须是可测的,而无需片外的线性AC信号或测量。ATE(自动测试设备)在离开工厂前,要做大量的校准与测试。要让BIST成为混合信号ATE的替代方案,就必须在使用前作校准与测试。采用基于扫描的测试,模拟BIST电路的纯数字部分应是可测的,包括逻辑BIST。如果数字电路包含了延迟线或延迟匹配线路,则应测试这些延迟和延迟增量。测量一个延迟的方法是:将延迟线包含或配置到一个回路振荡器振荡器振荡器是收发设备的基础电路,它的作用是产生一定频率的交流信号,是一种能量转换装置——将直流电能转换为

实用模拟BIST的基本原则,标签:电路设计,http://www.88dzw.com3 基础电路原则

3.1 原则一

通过施加时序不敏感的数字测试模式、时钟以及DC电压,测试机制本身必须是可测的,而无需片外的线性AC信号或测量。ATE(自动测试设备)在离开工厂前,要做大量的校准与测试。要让BIST成为混合信号ATE的替代方案,就必须在使用前作校准与测试。采用基于扫描的测试,模拟BIST电路的纯数字部分应是可测的,包括逻辑BIST。如果数字电路包含了延迟线或延迟匹配线路,则应测试这些延迟和延迟增量。测量一个延迟的方法是:将延迟线包含或配置到一个回路振荡器

振荡器

振荡器是收发设备的基础电路,它的作用是产生一定频率的交流信号,是一种能量转换装置——将直流电能转换为具有一定频率的交流电能。 [全文]

中,并用片上频率计数器测量其振荡频率。

对模拟BIST中纯 模拟部分的测试则更复杂。有些研究人员建议在自己的模拟BIST中使用一个ADC或DAC,暗含着ATE可以测试它的假设;然而,混合信号ATE仍将是必要的,因此削弱了BIST的很多优势。

也许最陈旧的BIST技术就是将一个DAC输出连回到一个ADC输入,或将一个调制器输出连到一个解调器

解调器

解调器是调制式直流放大电路中的一个重要组成部分.负责把已放大了的交流电压还原为直流电压,其大小和极性与交流电压的幅度和相位要对应。 [全文]

输入,以此完成整个数字测试。这种方法仿佛是用一个未经测试的电路,去测试另外的电路,对补偿失误不敏感。例如,对于ADC中补偿的相似非线性,DAC的非线性则可能过高,因为两者一起要好于任何单独一个。

www.88dzw.com3.2 原则二

模拟BIST的第二个原则是欠采样,即慢于Nyquist速率的采样,这意味着采样速率要低于最高频率的两倍——这对于较慢地分析一个信号是必需的。较慢的采样还有利于使BIST电路小于待测电路。

在有些自校准方法中,会用一个低速ADC去欠采样一只高速ADC或DAC的模拟信号。一级sigma-delta调制器是小而简单的模拟电路,如果带宽降低就可以将模拟信号转换为任意分辨率的数字码流。调制器可以采样一个1600万次/秒的信号,产生1600个1 bit的采样;调制器可以对这些采样作数字滤波,产生100万个4位分辨率采样/秒,或16000个16 位采样/秒,每种情况都将可用带宽减少至1/16。欠采样可以让一个较窄的兴趣带宽定位于原始信号频率的中心,使其转换为一个低的频率,从而更便于做分析。不过,欠采样也要付出混叠效应的代价,这是必须考虑的。

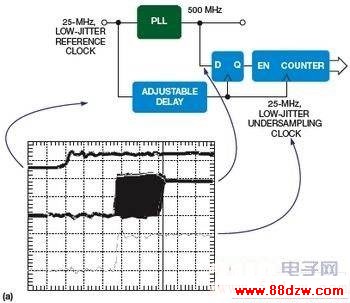

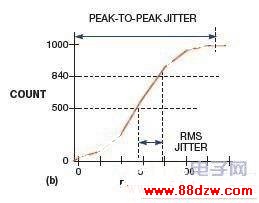

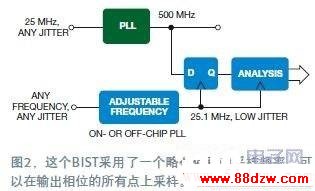

另一个采样的例子是一个PLL BIST,它使用PLL的输入基准时钟沿,去采样PLL的输出(图1a)。此时,一个基准通过一个可调延迟线,为一只锁存器提供时钟,锁存器完成采样工作。假设锁存器的输出计数1000个时钟周期,然后延迟递增。这个动作不断重复,直到锁存器获得了累加的分布函数(图1b)。PLL的输出频率可以比其基准频率高出很多倍。这种BIST不能检测到基准时钟沿之间的抖动,但另外一种采用略微偏移的采样频率的技术,可以在输出相位的所有点上作采样(图2)。

图1,PLL BIST使用PLL的输入基准时钟沿,采样PLL的输出 (a)。一个基准通过一根可调延迟线,为一个锁存器提供时钟,锁存器完成采样工作。锁存器的输出计数1000个时钟周期,然后延迟递增。这个动作不断重复,直到锁存器获得了累积分布函数 (b)。

- 上一篇:3V DAC在±10V中的应用

《实用模拟BIST的基本原则》相关文章

- › 实用模拟BIST的基本原则

- 在百度中搜索相关文章:实用模拟BIST的基本原则

- 在谷歌中搜索相关文章:实用模拟BIST的基本原则

- 在soso中搜索相关文章:实用模拟BIST的基本原则

- 在搜狗中搜索相关文章:实用模拟BIST的基本原则

当前位置:

当前位置: