一种频率特性测试仪的设计

[09-08 11:42:09] 来源:http://www.88dzw.com 其它电路 阅读:8771次

文章摘要: 3 主要功能电路设计 3.1 扫频信号发生器 AD9851是AD公司采用先进CMOS技术生产的具有高集成度的直接数字合成器,可以直接作为信号源,也可通过其内部的高速比较器转换为方波输出,作为灵敏的时钟产生器。它将相位累加器,波形存储器,10 Bit高速D/A集于一块芯片中,频带宽,频率精度和稳定度高,外围电路简单。 其内部结构如图2所示。AD9851内部的控制字寄存器首先寄存来自外部的频率、相位控制字,相位累加器接收来自控制字寄存器的数据后,决定最终输出的信号频率和相位,再经过内部D/A转换器,所得到的就是最终的数字合成信号。www.88dzw.com 设相位累加器的位

一种频率特性测试仪的设计,标签:电路设计,http://www.88dzw.com

3 主要功能电路设计

3.1 扫频信号发生器

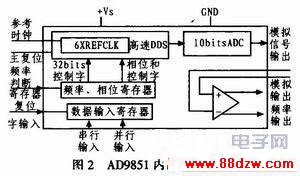

AD9851是AD公司采用先进CMOS技术生产的具有高集成度的直接数字合成器,可以直接作为信号源,也可通过其内部的高速比较器转换为方波输出,作为灵敏的时钟产生器。它将相位累加器,波形存储器,10 Bit高速D/A集于一块芯片中,频带宽,频率精度和稳定度高,外围电路简单。

其内部结构如图2所示。AD9851内部的控制字寄存器首先寄存来自外部的频率、相位控制字,相位累加器接收来自控制字寄存器的数据后,决定最终输出的信号频率和相位,再经过内部D/A转换器,所得到的就是最终的数字合成信号。

设相位累加器的位数为N,相位控制字的值为FN,频率控制字的位数为M,频率控制字的值为FM,内部工作时钟为Fc,最终合成信号的频率和相位可由下式来决定:F=Fc·FM/2N,θ=2πFN/2M。其中M=32,N=5,外部输入25 MHz的时钟,经过内部6倍频后为fc=150 MHz。由于不需要设置相位,所以五位相位控制字一直写入0,频率控制字为FM=2NxF/Fc。

3.2 有效值检波模块

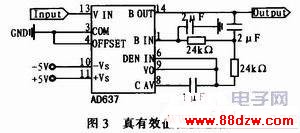

真有效值检波电路采用ADI公司的AD637,该芯片根据真有效值计算公式,直接输出信号的有效值电压,原理图如图3所示,通过使用片内后级滤波网络可以有效减小带内纹波。在C_AV口接入1μF的电容,在输入信号频率小于1MHz时,幅度的测量误差小于1%。精度非常高。

3.3 限幅放大电路

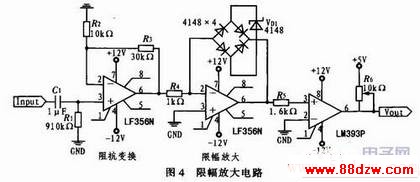

在对信号进行相位测量前,要先将其整形为方波。但当信号经被测网络后幅值有较大变化,可能出现信号较强时超出后级处理芯片的测量范围,而信号较弱时又不能够被后级处理芯片识别的情况。由于对信号进行频率或者相位的测量只需要知道其周期信息,而非幅值信息,因此在把正弦信号整形成方波的模块中,采取限幅放大,而不采用单纯的LM311整形电路,可以达到更好的效果。

具体电路如图4所示,此限幅放大电路由前级同相放大、限幅放大和电平转换电路3部分组成。前级同相放大电路主要起到阻抗变换的作用;限幅放大电路采用二极管1N4148实现负反馈桥式限幅。如果输出信号幅值大于5 V,桥式电路的二极管导通,稳压二极管工作,将电压钳位于5 V左右;电平转换电路将放大后的信号经比较后整形为方波信号。转换为TTL电平,便于送入后级电路处理。

由于比较器一级的输入输出电压都很大,因此电路中的运放芯片应该选取超高摆率、输出电流大、耐压高的运放。同时,为使进入比较器的信号更加稳定,应选取增益带宽积较大的运放。综合以上因素,选取LF356。其增益带宽积达到5MHz,摆率12V/μs,远满足设计要求。

4 系统软件的设计

系统软件设计部分基于单片机及FPGA为平台,完成了键盘输入、幅值测量、相位测量以及示波器显示扫频信号的功能。键盘输入设置扫频范围和频率步进。幅值测量由10位串行AD/C TLV1544实现,相位测量由40 M晶振计数,测量精度高。测量数据存于FPGA的RAM中,通过双通道TLV5638输出。系统提供两种显示方式,一种是通过示波器显示整个被测网络的幅频和相频曲线,一种是通过LCD显示特定输入频率的幅值和相位。由于系统采用的AD9851,TLV1544和TLV5638全部是串行控制的,导致程序有些复杂,需要严格控制好时序,否则容易出问题。同时考虑到程序的时间效率,应避免冗余代码,在能用移位运算的情况下避免使用乘除运算。扫频测量流程如图5所示。

《一种频率特性测试仪的设计》相关文章

- › 一种频率特性测试仪的设计

- 在百度中搜索相关文章:一种频率特性测试仪的设计

- 在谷歌中搜索相关文章:一种频率特性测试仪的设计

- 在soso中搜索相关文章:一种频率特性测试仪的设计

- 在搜狗中搜索相关文章:一种频率特性测试仪的设计

当前位置:

当前位置: