利用RapidIO技术搭建的可重构信号处理平台

[10-10 20:38:44] 来源:http://www.88dzw.com 单片机学习 阅读:8440次

文章摘要:参考文献[1] FULLER S.RapidIO:The embedded system interconnect. Wiley,ISBN:978-0-470-09291-0,US.,2005.[2] RapidIO Trade Association.RapidIO interconnect Specification Rev.2.0.www.rapidio.org,2008.[3] BOUVIER D,RapidIO:The interconnect architecture for high performance embedded systems.www.rapidio.org,200

利用RapidIO技术搭建的可重构信号处理平台,标签:单片机开发,单片机原理,http://www.88dzw.com参考文献

[1] FULLER S.RapidIO:The embedded system interconnect. Wiley,ISBN:978-0-470-09291-0,US.,2005.

[2] RapidIO Trade Association.RapidIO interconnect Specification Rev.2.0.www.rapidio.org,2008.

[3] BOUVIER D,RapidIO:The interconnect architecture for high performance embedded systems.www.rapidio.org,2009.

[4] Altera Corparation.RapidIO megacore function user guide. www.altera.com,2008.

[5] Altera Corparation.Avalon interface specification.www.altera.com,2008. www.88dzw.com

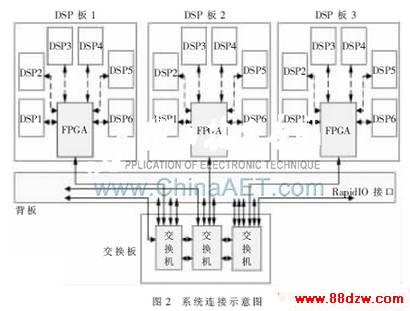

2.2 板卡间DSP的连接结构

在DSP板板卡之间用RapidIO接口连接有很多好处。最直接的好处是,由于RapidIO采用的是串行总线,这使得背板上的布线设计不再困难,系统可以扩展得更大。更重要的是,由于RapidIO是以数据包的格式传送数据的,用户可以通过改变数据包包头中的路由信息来改变数据的流向。这使得系统的重构变得十分容易。DSP板在系统中的连接如图2所示。

在系统内, 任意2片(不同板卡上的)DSP芯片之间都可以建立连接。例如:如果用户想要将DSP板1上的DSP4中的数据发送给DSP板3上的DSP6,只需在系统上电时提前将DSP板1上的FPGA内部控制路由的寄存器(目标板ID号设为3,目标DSP分配的地址设置为6)通过软件设置好即可。交换机收到数据后,会根据数据包中用户配置的路由信息将数据包送往目标DSP板,然后,目标DSP板上的FPGA进一步将数据发送到目标DSP芯片。在下一次的算法设计中,如果数据的流向改变很大时,用户可以根据数据流向的特点,重新优化DSP网络的拓扑结构,以适应不同的算法。

重构DSP网络拓扑的过程在传统的信号处理平台中是很难实现的。在多数情况下,由于DSP拓扑结构不够灵活,算法设计者受限于固定的DSP拓扑结构,只能降低系统的使用效率,从而使大量的DSP资源闲置,降低了系统的处理能力。而在这种新的信号处理平台架构中,用户只需要通过软件界面设置路由信息即可完成整个平台结构的改变,系统不会因为算法的改变而降低使用效率。

Tag:单片机学习,单片机开发,单片机原理,维修教程知识 - 单片机学习

- 上一篇:基于MCU设计的离线锂电池充电器

《利用RapidIO技术搭建的可重构信号处理平台》相关文章

- › 利用RapidIO技术搭建的可重构信号处理平台

- 在百度中搜索相关文章:利用RapidIO技术搭建的可重构信号处理平台

- 在谷歌中搜索相关文章:利用RapidIO技术搭建的可重构信号处理平台

- 在soso中搜索相关文章:利用RapidIO技术搭建的可重构信号处理平台

- 在搜狗中搜索相关文章:利用RapidIO技术搭建的可重构信号处理平台

最新更新

当前位置:

当前位置: