嵌入式处理器MPC8272与外设的息线适配

[10-10 20:36:41] 来源:http://www.88dzw.com 电子制作 阅读:8612次

文章摘要:MPC8272是Motorola公司2004年推出的第2代PowerQUICC通信处理器。该通信处理器采用MPC603e核心处理器,核心处理器工作频率达400 MHz,外部总线工作频率达100 MHz,总线支持32位地址,64位数据位宽操作。另外该通信处理器内嵌一个32位RISC处理器的通信处理模块,集成有MAC、FCC、SMC、ATM、HDLC、UART、T1、USB、PCI等设备通信接口,以及1个60x总线接口连接通用外围设备,非常适用于通信控制领域的应用。1 通信处理器MPC8272读写时序 MPC8272总线对外部器件的读、写访问是通过存储器控制模块来实现的,存储器控制模块生成8

嵌入式处理器MPC8272与外设的息线适配,标签:电子小制作,http://www.88dzw.comMPC8272是Motorola公司2004年推出的第2代PowerQUICC通信处理器。该通信处理器采用MPC603e核心处理器,核心处理器工作频率达400 MHz,外部总线工作频率达100 MHz,总线支持32位地址,64位数据位宽操作。另外该通信处理器内嵌一个32位RISC处理器的通信处理模块,集成有MAC、FCC、SMC、ATM、HDLC、UART、T1、USB、PCI等设备通信接口,以及1个60x总线接口连接通用外围设备,非常适用于通信控制领域的应用。

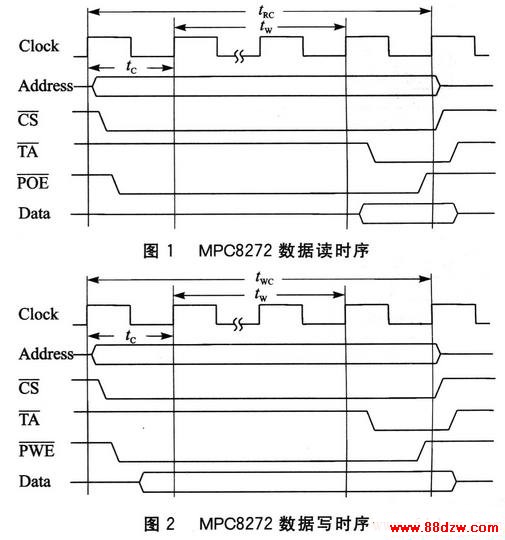

1 通信处理器MPC8272读写时序

MPC8272总线对外部器件的读、写访问是通过存储器控制模块来实现的,存储器控制模块生成8个外部存储器地址空间片选信号CSO~CS7,每个片选信号对应2个主要控制寄存器BR和OR,用它们来定义片选信号所定义的地址空间和对等待状态数、读写选通信号的建立时间、激活时间、保持时间等的设置。MPC8272对外部器件数据读、写时序如图1、图2所示。其中tc是外部总线工作时钟Clock的时钟周期,tRC和tWC分别是读写指令周期,tW是读写指令周期内插入的Clock时钟周期。当不使用外部输入信号TA(数据传输确认信号)时,插入的时钟周期数由0R寄存器的SCY值确定,其值最大为15个时钟周期;当使用外部输入信号TA时,插入的时钟周期数由其确定;当输入信号TA变低时(即外设数据准备好时),处理器即可完成此次数据的读写操作。

MPC8272的外部总线工作频率可达100 MHz。当读写指令周期不插入时钟周期时,其外部总线指令周期为2个时钟周期――20 ns,外部总线速率最高可达(50×N)Mbps(其中N为总线数据位宽)。该速率对于一般通用外设来说是很高的,需调整OR寄存器的SCY值以降低总线速率与外设进行读写操作。插入最大15个时钟周期时,外部总线指令周期最大为17个时钟周期――170 ns,此时外部总线速率最低为(5.8×N)Mbps,该速率满足常用外设的总线读写要求。对于通信的一些特殊外设,如交换网络电路MT90826、双口RAM IDT71V321、数字信号处理器TMS320VC5416等接口,需采用处理器MPC8272的外部数据传输确认信号TA并设计相应的外部硬件等待逻辑电路进一步降低总线速率或动态插入任何数目的等待时钟周期tW,以避免数据读写冲突,提高处理器总线效率和数据传输可靠性。

2 外设读写时序分析

作为语音通信产品,嵌入式处理器主要外设的工作是:话音交换矩阵完成话音交换;DSP完成DTMF收发号、FSK来电号码显示以及会场话音融合等;双口RAM完成嵌入式处理器与其他处理器间的数据通信;显示器用于参数设置或功能显示等。各外设的总线接口具有读、写周期长且不确定等特点,不能直接与MPC8272总线连接,需设计相应的外部硬件电路以满足外设的读写时序要求。以下分别对各外设接口进行介绍。

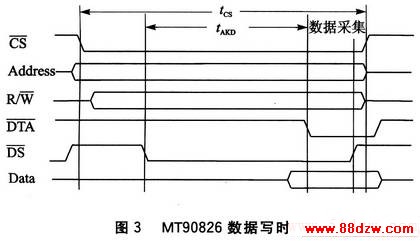

MT90826是卓联公司开发的4 096×4 096通道无阻塞大型话音交换矩阵电路,支持2.048 Mbps、4.096 Mbps、8.192Mbps和16.384.Mbps等ST―BUS格式数据流。电路采用顺序写入控制读出交换机理,每个输出通道对应一个连接寄存器。嵌入式处理器通过在输出通道的连接寄存器中写入输入通道的地址,完成输入与输出通道话音数据流的交换。嵌入式处理器对MT90826的读写操作是否完成,可通过MT90826的数据传输确认信号DTA指示,其时序如图3所示。当DTA信号在片选周期内由高变低后,表示嵌入式处理器可以结束本次总线的读写操作了。tAKD时间长短并不确定,其最大值为240 ns,最小值为0。

图7中,TA_N是MPC8272的数据传输确认信号,低电平有效,而DSP HPI接口数据准备好信号HRDY高电平有效,因此须反向;双口RAM忙指示信号(即数据未准备好)BUSY_N低电平有效,须反向;OLED_RDY_N是当外部总线为100 MHz时(SCLK为100MHz外部总线时钟输入),插入cnt=100个时钟周期(等待状态为1μs)后的数据准备好信号,低电平有效。功能模块RDY_N的相关VHDL描述如下:

《嵌入式处理器MPC8272与外设的息线适配》相关文章

- › 基于双嵌入式处理器的高清数字电视设计

- › 用CS43L42音频解码器和EP7212嵌入式处理器设计的MP3文件播放系统

- › 嵌入式处理器MPC8272与外设的息线适配

- 在百度中搜索相关文章:嵌入式处理器MPC8272与外设的息线适配

- 在谷歌中搜索相关文章:嵌入式处理器MPC8272与外设的息线适配

- 在soso中搜索相关文章:嵌入式处理器MPC8272与外设的息线适配

- 在搜狗中搜索相关文章:嵌入式处理器MPC8272与外设的息线适配

当前位置:

当前位置: