视频监控系统中多画面处理器的设计

[09-14 01:01:55] 来源:http://www.88dzw.com 电子制作 阅读:8975次

文章摘要: 近年来,随着视频监控系统在各个领域的广泛应用,作为视频监近系统组成之一的多画面处理器的应用也愈来愈普遍。如使用一台九画面处理器,则可在一台监视器上同时监控9个目标,只需使用一台录像机便可对9路视频信号同时实时录像。目前多画面处理器有黑白/彩色四、九、十六画面处理器等6种类型。一般说来,多画面处理器除了有画面分割功能外,还须有视频信号切换及报警功能。视频信号功换功能是指多画面处理器有一路视频输出是输入视频信号或画面分割信号的顺序切换,且切换时间可调;报警功能是指多画面处理器能输入、输出报警信号,报警时相应的画面上叠加有报警信息,并将报警信息存储起来以便日后查阅。设计多画面处理器可使用专

视频监控系统中多画面处理器的设计,标签:电子小制作,http://www.88dzw.com近年来,随着视频监控系统在各个领域的广泛应用,作为视频监近系统组成之一的多画面处理器的应用也愈来愈普遍。如使用一台九画面处理器,则可在一台监视器上同时监控9个目标,只需使用一台录像机便可对9路视频信号同时实时录像。目前多画面处理器有黑白/彩色四、九、十六画面处理器等6种类型。一般说来,多画面处理器除了有画面分割功能外,还须有视频信号切换及报警功能。视频信号功换功能是指多画面处理器有一路视频输出是输入视频信号或画面分割信号的顺序切换,且切换时间可调;报警功能是指多画面处理器能输入、输出报警信号,报警时相应的画面上叠加有报警信息,并将报警信息存储起来以便日后查阅。设计多画面处理器可使用专用DSP芯片,这样虽然满足了速度要求,但开发周期较长,产品的调试、修改及升级比较困难,成本较高。由于FPGA(即现场可编程门阵列)器件具有集成度高、体积小、功耗低、设计灵活且价格较低,有快速高效的开发平台,可加快开发周期等优势,因此目前多画面处理器的设计基本上采用FPGA作为其中的视频信号处理器件。由于FPGA的功能由其内部的编程数据确定,编程数据的装载方法之一是上电后由单片机实现,因此多画面处理器含有单片机。一方面利用单片机在上电后将FPGA所需的编程数据写入FPGA中,另一方面视频信号的切换、字符叠加及报警信息的处理也由单片机来完成。下面具体介绍基于FPGA器件和单片机的黑白四画面处理器的设计方法。

1 黑白四画面处理器的组成及主要功能

1.1 黑白四画面处理器的组成

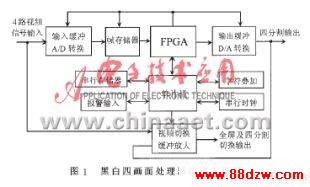

黑白四画面处理器的方框图如图1所示。由图1可知,该多画面处理器以FPGA器件和单片机为核心,外加A/D、D/A、帧存储器、串行存储器、串行时钟和字符叠加等辅助芯片组成。

1.2黑白四画面处理器的主要功能

该四画面处理器主要功能如下:

・视频格式为CCIR模式,即视频信号的场频为50Hz;

・双工操作(在录像的同时可进行回放),菜单设定;

・全屏显示时象素为1024×512,256个灰度等级;

・4路CVBS输入及1路录像输入;

・1路全画面与四分割切换输出,1路录像输出(固定四分割);

・切换时间可调,范围为1~255s。

・画面上可叠加时间日期,且位置可调整;

・有报警输入输出功能,报警复位时间的可调范围为1~300s;

・有视频信号丢失报警功能,报警时对应的画面上有文字显示。

www.88dzw.com2.5 单片机

单片机选日本NEC公司的μPD78F0034,该芯片的主要特点是:

・时钟为8.38MHz时的指令周期为0.24μs;

・ROM为32KB FLASH,RAM为1024bytes;

・可寻址空间为64KB,5个外部中断,15个内部中断;

・39个CMOS I/O,8个COMS INPUT,4个N-CH漏极开路I/O;

・1个16位定时/计数器,2个8位定时/计数器;

・1个时钟定时器,1个看门狗定时器,1个UART端口;

・支持I2C总线,有时钟信号及蜂鸣信号输出功能;

・外部数据总线8位,内部寄存器为16位;

・有8位无符号乘法指令,16位除法指令;

・工作电压范围为1.8V~5.5V,有STOP/HALT工作模式。

由此可见,该芯片的性能要优于目前流行的MCS-51系列,其8位无符号乘法指令及16位除法指令给软件编程带来了很大的方便。另外,由于该芯片本身带看门狗定时器,因而无需外加看门狗电路,就能保证系统稳定、可靠地工作。

2.6 存储器

存储器芯片采用串行EEPROM芯片X24C16。该芯片是容量为2KB带写保护的I2C总线数据存储器,当WP=1时,只能读,不能写数据。它使用串行数据线(SDA)和串行时钟线(SCL)进行主从器件之间的数据传输。I2C总线上的数据传输率可达100Mbps,快速方式下可达400Mbps。在I2C总线传输中,开始和停止条件定义如下:当SCL为高时,SDA由高变低为开始条件;当SCL为高时,SDA由低变高时为停止条件(如图3(a)所示)。SDA和SCL都是双向传输线,SDA线上的数据在时钟为高期间必须是稳定的,只有当SCL线上的时钟信号为低时,数据线上的状态才可以改变(如图3(b)所示)。输出到SDA线上的每一字节必须是8位,每次传输的字节不受限制,每字节必须有一个应答位。本设计中X24C16的第5脚(SDA)和第6脚(SCL)分别接单片机的P3.6和P3.7。

《视频监控系统中多画面处理器的设计》相关文章

- › 呔!你这毛贼哪里走 安保视频监控系统搭建指南

- › 基于互联网音视频的手机视频监控幼儿园应用方案

- › 手机视频监控功能介绍以及应用范围

- › 视频监控网络技术之IP地址

- › 基于MPEG-4和RTP的网络视频监控系统研究

- › 家庭网络视频监控技术的应用前景

- 在百度中搜索相关文章:视频监控系统中多画面处理器的设计

- 在谷歌中搜索相关文章:视频监控系统中多画面处理器的设计

- 在soso中搜索相关文章:视频监控系统中多画面处理器的设计

- 在搜狗中搜索相关文章:视频监控系统中多画面处理器的设计

编辑推荐

- ・ 自制教室照明节电控制器

- ・ 双色音乐彩灯的制作

- ・ 三相交流电机缺相保护器

- ・ 声光控节能灯的制作

- ・ 同线电话转呼及互通器电路

- ・ 超低频信号发生器的制作

- ・ 自制热转印电路板

- ・ 警笛发声生器电路

- ・ 一款节能电路

- ・ 利用太阳能充电的旅行充电器

当前位置:

当前位置: