视频监控系统中多画面处理器的设计

[09-14 01:01:55] 来源:http://www.88dzw.com 电子制作 阅读:8975次

文章摘要:4 软硬件设计时要注意的几个问题(1)使用帧存储器AL422应注意的问题 ・由于帧存储器AL422是FIFO DRAM,因而须确保WCK和RCK信号始终有且信号的频率不低于1MHz,因WCK和RCK中频率较高者将作为DRAM的刷新时钟信号。・在AL422的/RRST信号的上升沿,/RE信号不能为低,这一点在确定FPGA的编程数据时要特点注意(因/RRST和/RE信号均由FPGA提供);・AL422可在5V或3.3V电源电压下工作,当使用5V电源时,其DEC脚(Pin19)须接2.2μF的去耦电容;当使用3.3V电源时,DEC脚(Pin19)可直接与3.3V相连,并通过0.1μF电容旁路到地;电

视频监控系统中多画面处理器的设计,标签:电子小制作,http://www.88dzw.com4 软硬件设计时要注意的几个问题

(1)使用帧存储器AL422应注意的问题

・由于帧存储器AL422是FIFO DRAM,因而须确保WCK和RCK信号始终有且信号的频率不低于1MHz,因WCK和RCK中频率较高者将作为DRAM的刷新时钟信号。

・在AL422的/RRST信号的上升沿,/RE信号不能为低,这一点在确定FPGA的编程数据时要特点注意(因/RRST和/RE信号均由FPGA提供);

・AL422可在5V或3.3V电源电压下工作,当使用5V电源时,其DEC脚(Pin19)须接2.2μF的去耦电容;当使用3.3V电源时,DEC脚(Pin19)可直接与3.3V相连,并通过0.1μF电容旁路到地;电容均使用钽电容。由于使用3.3V时,器件功耗低,且受噪声干扰小,因而在本设计中采用了3.3V电源对AL422供电。

(2)为避免视频信号之间的串扰,各种模拟视频信号间均用较粗的地线隔开,且视频走线足够宽。

以上介绍了黑白四画面处理器的设计。为了节省线路板空间并使产品小巧玲珑,所有的元器件及IC芯片均选用贴片式封装。鉴于篇幅的限制,本文没有讨论多画面处理器软件方面的设计。至于9画面和16画面处理器的设计,其设计思想及组成方框图与该4画面处理器相类似,只不过要增加A/D、AL422及FPGA,软件编程也复杂一些。

www.88dzw.com2 各部分电路的结构及工作原理

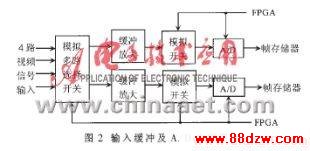

2.1 输入缓冲及A/D转换

该部分电路的主要功能是将输入的模拟视频信号转换成数字视频信号供FPGA器件处理,其方框图如图2所示。4路视频信号经过受FPGA控制的模拟多路选择器后,输出2路视频信号,经过缓冲放大后送到受FPGA控制的模拟开关;然后再输出给A/D,2路视频信号需要2片A/D芯片。A/D芯片选TLC5510,该芯片是一种分辨率为8位、20MSPS(20兆采样点/秒)的CMOS模/数转换器。在FPGA的控制下,TLC5510将输入的模拟视频信号转换成数字视频误,然后送往帧存储器。

2.2 帧存储器

帧存储器选AVERLOGIC公司的AL422,共需要2片。AL422是存储量为384KB×8Bits的FIFO(First In First Out)DRAM,它支持VGA、CCIR、NTSC、PAL和HDTV分辨率,具有独立的读/写操作及输出使能控制;存储时间为15ns的高速异步串行存取,可在5V或3.3V电源电压下工作,标准的28脚SOP封装。

2.3 FPGA器件

FPGA是本设计的核心,与传统逻辑电路和门阵列相比具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,D触发器再来驱动其它逻辑或驱I/O。这些模块利用金属连线互相连接或连接到I/O模块。FPGA通过向内部静态存储单元加载编程数据来实现其FPGA通过向内部静态存储单元加载编程数据来实现其逻辑,存储在存储单元中值决定了FPGA实现的功能;FPGA的这种结构允许无限次的重新编程。由此可见,用FPGA设计的产品调试修改及升级均很容易,且具有很大的灵活性。目前FPGA的种类很多,在本设计中选用Spartan系列的XCS05XL。该芯片是Xilinx公司推出的低价格、高性能的FPGA,其主要特点如下:

・系统门的数目达到了5000,Logic cell数目达到了238,系统资源丰富;

・具备片上可编程分布式RAM,最多可编程的RAM达3200bit;

・分布式算术逻辑单元,支持分布式DSP运算;

・灵活的高速时钟网络,内部三态总线;工作电压为3.3V。

有关XCS05XL的详细资料请参阅参考文献[1]。

FPGA的编程数据存储在单片机的FLASH ROM里。每次上电后单片机将编程数据装入XCS05XL,编程模式选从串模式,因而其22脚(M1)和24脚(M0)悬空。编程数据装入后,XCS05XL的逻辑功能就确定了;XCS05XL控制视频信号的输入及A/D转换,在其内部将每路视频信号压缩为原来的1/2,同时在单片机的控制下给每路叠加时间、日期、通道数字字符信息,然后将压缩的四路视频信号合成为一路完整的数字视频信号,并输出给D/A,形成四分割输出。

2.4 D/A转换及输出缓冲放大

D/A转换电路将FPGA输出的数字视频信号转移成模拟视频信号,然后经过缓冲放大输出给监视器,D/A芯片选HI1171。该芯片是一种分辨率为8位,频率为40MHz的高速D/A转换器,其最大积分和微分线性误差分别为1.3LSB和0.25LSB;最小建立时间仅为5ns,在单5V下工作,功耗只有80mW。输出缓冲放大由分立元件组成。

《视频监控系统中多画面处理器的设计》相关文章

- › 呔!你这毛贼哪里走 安保视频监控系统搭建指南

- › 基于互联网音视频的手机视频监控幼儿园应用方案

- › 手机视频监控功能介绍以及应用范围

- › 视频监控网络技术之IP地址

- › 基于MPEG-4和RTP的网络视频监控系统研究

- › 家庭网络视频监控技术的应用前景

- 在百度中搜索相关文章:视频监控系统中多画面处理器的设计

- 在谷歌中搜索相关文章:视频监控系统中多画面处理器的设计

- 在soso中搜索相关文章:视频监控系统中多画面处理器的设计

- 在搜狗中搜索相关文章:视频监控系统中多画面处理器的设计

编辑推荐

- ・ 自制教室照明节电控制器

- ・ 双色音乐彩灯的制作

- ・ 三相交流电机缺相保护器

- ・ 声光控节能灯的制作

- ・ 同线电话转呼及互通器电路

- ・ 超低频信号发生器的制作

- ・ 自制热转印电路板

- ・ 警笛发声生器电路

- ・ 一款节能电路

- ・ 利用太阳能充电的旅行充电器

当前位置:

当前位置: