PXA270嵌入式系统设计(2)―时钟及复位部分

[11-20 15:53:51] 来源:http://www.88dzw.com arm嵌入式 阅读:8888次

文章摘要:作者:刘洪涛,www.88dzw.com嵌入式培训中心高级讲师,ARM ATC授权培训讲师。最近计划针对我们www.88dzw.com的教学开发一套PXA270系统,我把我的一些软、硬件开发过程记录下来和大家一起分享、讨论。有好的建议大家一定要及时交流,lht@farsight.com.cn。上一篇我写了“PXA270嵌入式系统设计一:电源管理部分”,今天接着写一下关于时钟及复位部分的内容,欢迎指正~~一、时钟部分任何一款处理器都需要至少一个时钟源。在处理器的内部会有相应的时钟管理单元来为cpu及各个功能控制单元提供合适的时钟。PXA270处理器的需要两个外部振荡器,1个13M和1个32.76

PXA270嵌入式系统设计(2)―时钟及复位部分,标签:arm嵌入式系统,arm系统,http://www.88dzw.com

作者:刘洪涛,www.88dzw.com嵌入式培训中心高级讲师,ARM ATC授权培训讲师。

最近计划针对我们www.88dzw.com的教学开发一套PXA270系统,我把我的一些软、硬件开发过程记录下来和大家一起分享、讨论。有好的建议大家一定要及时交流,lht@farsight.com.cn。上一篇我写了“PXA270嵌入式系统设计一:电源管理部分”,今天接着写一下关于时钟及复位部分的内容,欢迎指正~~

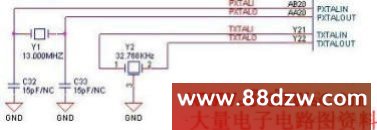

一、时钟部分

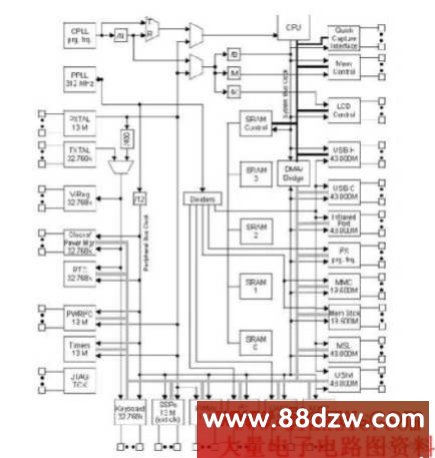

任何一款处理器都需要至少一个时钟源。在处理器的内部会有相应的时钟管理单元来为cpu及各个功能控制单元提供合适的时钟。

PXA270处理器的需要两个外部振荡器,1个13M和1个32.768K。它们各自的作用:

13M的时钟主要用于产生系统各个PLL的参考时钟,也可以为部分低速控制器提供时钟;

32.768K的时钟主要用于为RTC控制器提供实时时钟源,也可以为部分低速控制器提供时钟。

PXA270处理器内部有两个PLL单元,一个是外围PLL,另一个是核心PLL

外围PLL使能后产生固定的312M时钟,用于为高速控制器提供时钟源;

核心PLL可以产生26―*M时钟,用于cpu、内存控制器、系统总线、及LCD控制器。

时钟部分的电路原理图:

二、复位部分

PXA270提供了5种复位方式:

上电复位:当VCC_BATT管脚第一次上电时产生,是一种完全复位。

硬件复位:也是种完全复位,当nRESET管脚置位时产生。

看门狗复位:看门狗控制器触发,是一种部分复位,详见PXA270芯片手册。

GPIO复位:是硬件复位的一种形式,可以由外部信号触发。也是一种完全复位。

睡眠退出复位:复位那些在睡眠和深度睡眠时断电的模块。

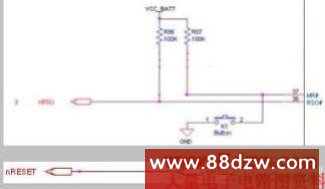

系统中和复位相关的电路原理图。

上电复位

硬件复位

下图是max1586C和系统复位电路相关的接线

K1为复位按键,通过max1586C的复位管理电路输出nRSO信号。如果系统没有类似max1586C的复位管理电路的话,可以用一片类似max811的复位芯片来完成,也可以用阻容及一些逻辑电路的方式来完成复位。

注意:max1586C的MR脚复位会复位max1586C的V3输出到1.3V,对其它电压输出没有影响。

下图是复位信号和PXA270的nRESET的接线。

当nRESET置位或看门狗控制器复位时,nRESET_O都可以置位。可以用其来完成其它外围芯片的复位。

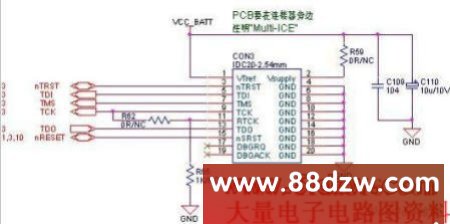

下图是JTAG电路,其复位信号要和系统的nRESET连接。

时钟复位部分大致就这么多了。

“www.88dzw.com提供”

《PXA270嵌入式系统设计(2)―时钟及复位部分》相关文章

- › PXA270的LCD显示系统的设计与实现

- › 基于PXA270的LCD显示系统的设计与实现

- › 基于PXA270的电子纸显示系统

- › 基于PXA270的移动天文观测系统设计

- › 基于Intel PXA270的WinCE操作系统移植

- › PXA270嵌入式系统设计(2)―时钟及复位部分

- 在百度中搜索相关文章:PXA270嵌入式系统设计(2)―时钟及复位部分

- 在谷歌中搜索相关文章:PXA270嵌入式系统设计(2)―时钟及复位部分

- 在soso中搜索相关文章:PXA270嵌入式系统设计(2)―时钟及复位部分

- 在搜狗中搜索相关文章:PXA270嵌入式系统设计(2)―时钟及复位部分

当前位置:

当前位置: