高速HDI电路板设计过程的考虑(推荐)

[08-09 20:40:07] 来源:http://www.88dzw.com CAD CAM 阅读:8653次

文章摘要: Seraphim Wiring Factor 根据线路需求的评估,不同线路的容量是可以预测的,设计规则和叠层结构则决定了这个容量。下表为当前产业界的能力: 特点 传统PCB 传统HP-HDI PBGA/MCML HDI 高I/O的倒装芯片 最小线宽(mil) 4 5 3 1.6 最小线距(mil) 4 5 3 2.0 最小焊盘间距(mil) 14 20 10 9.3 焊盘最小直径(mil) 20 12-14 12 4-5 过孔形成方法 机械钻孔 光致成孔/激光成孔 光致/激光/等离子成孔 多束激光成孔 最小过孔直径(mil) 10 4-6 3-7 2.5-3.5 焊盘表面处理

高速HDI电路板设计过程的考虑(推荐),标签:CAD教程,CAM资料,http://www.88dzw.comSeraphim Wiring Factor

根据线路需求的评估,不同线路的容量是可以预测的,设计规则和叠层结构则决定了这个容量。下表为当前产业界的能力:

特点

传统PCB

传统HP-HDI

PBGA/MCML HDI

高I/O的倒装芯片

最小线宽(mil)

4

5

3

1.6

最小线距(mil)

4

5

3

2.0

最小焊盘间距(mil)

14

20

10

9.3

焊盘最小直径(mil)

20

12-14

12

4-5

过孔形成方法

机械钻孔

光致成孔/激光成孔

光致/激光/等离子成孔

多束激光成孔

最小过孔直径(mil)

10

4-6

3-7

2.5-3.5

焊盘表面处理

SOS Bumps

所有

Ni-Au

Microbumps

目前产业界生产能力比较

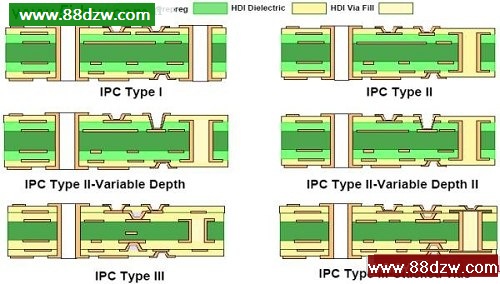

图 2-6 描述了最常见的HDI结构,这六种结构遵循了最新的IPC-2315规范,最前面的四类使用频率最高。

Fig2-6 高性能HDI多层板中最常见结构

2.5 组装过程的考虑

设计中需要考虑的最后一个因素就是组装工艺,如下四个必要的设计特点需要考虑进去:

在线测试性

SMT组装间距

板面大小(关系到印刷焊料钢板大小)

返修

如果采用了VIP工艺,那么在线测试的可行性则成为最主要的挑战。这是因为对大的面积阵列元件,VIP技术无法使用突破模式,而是直接嵌入到板内,所以添加测试盘必须考虑到不能损害信号完整性,同时由于X-Y向的热膨胀系数的改变,所以也要注意组装后的板面尺寸变化。如果板面尺寸较大并且印刷焊料的钢板工作片的参考数据点是以一个拐角为基准的,那么在径向每一线性英寸的改变将会使板面尺寸与其它拐角产生0.4英寸的偏差;对一片12inch×16inch板而言,在它较远的拐角则可能产生高达5―7mil的偏差。如果采用了细间距的uBGA,这将是焊接不良的主要原因,对这类器件而言是无法返修的。

要想返修比较可行,基材特性显得尤为重要,在拆卸元件、重焊焊盘以及重新安装新器件的时候,基材要能经受住集中的热冲击还不能导致剥离。

3. 结论

高性能HDI类产品是复杂元件的载体,这类产品具有如下特点:有高的I/O数、更精细的间距、电路的运行频率极高和信号上升时间很快。这样就对信号完整性要求非常严格,自然的也对基材要求严格,过孔结构、叠层方案、设计规则的选择更加复杂。

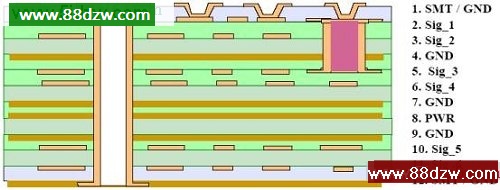

通过图3-1可以了解所有这些驱动力的优点,该图显示的是一个12层HDI的第一类多层板,该板中有四层具有埋孔,第一到第五层有盲孔。该板就用于连接六片有1247个I/O 陶瓷焊料柱的阵列器件(1.0mm 的间距),与该板具有等效功能的通孔多层板的层数则会高达24层,对连接系统而言,这样的厚度太厚,而且还将导致过多的噪声和信号损失等不良后果。

Fig3-1 12 层HDI高性能多层板图例

编辑:(tanjunrong)

- 上一篇:PCB尺寸和外形的设计

《高速HDI电路板设计过程的考虑(推荐)》相关文章

- › 高速HDI电路板设计过程的考虑(推荐)

- 在百度中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

- 在谷歌中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

- 在soso中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

- 在搜狗中搜索相关文章:高速HDI电路板设计过程的考虑(推荐)

当前位置:

当前位置: