感性加载的反射

[09-12 11:24:08] 来源:http://www.88dzw.com 电路基础 阅读:8244次

文章摘要:串接到均匀传输线上任何部件都会有一些串联电感。这些电感可能会出现在路径的末端,如器件的封装引线或是串联终端电阻的寄生电感,也可能出现在线路的中途,如参考平面的分割导致信号返回路径上有一小段间隙就会引入一个串联电感,以图1所示的模型来说明感性突变产生的反射。图1 电感性负载的反射分析模型如果末端元件的封装引脚存在一个寄生串联电感L,路径时延为1 ns,电感为2 nH和10 nH时接收端电压波形如图2所示。可见,当引线电感较大时,接收端信号电压会发生严重的振铃,轴向引线电阻的串联寄生电感约为10 nH,如果使用在该系统中会带来严重的问题,而应该改用"SMD"元件。如果传输线末端

感性加载的反射,标签:电子电路基础,模拟电路基础,http://www.88dzw.com 串接到均匀传输线上任何部件都会有一些串联电感。这些电感可能会出现在路径的末端,如器件的封装引线或是串联终端电阻的寄生电感,也可能出现在线路的中途,如参考平面的分割导致信号返回路径上有一小段间隙就会引入一个串联电感,以图1所示的模型来说明感性突变产生的反射。

图1 电感性负载的反射分析模型

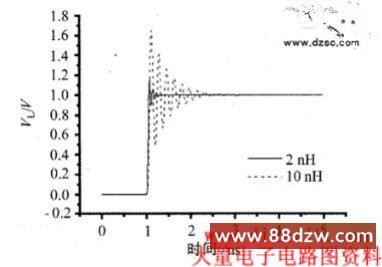

如果末端元件的封装引脚存在一个寄生串联电感L,路径时延为1 ns,电感为2 nH和10 nH时接收端电压波形如图2所示。

可见,当引线电感较大时,接收端信号电压会发生严重的振铃,轴向引线电阻的串联寄生电感约为10 nH,如果使用在该系统中会带来严重的问题,而应该改用"SMD"元件。

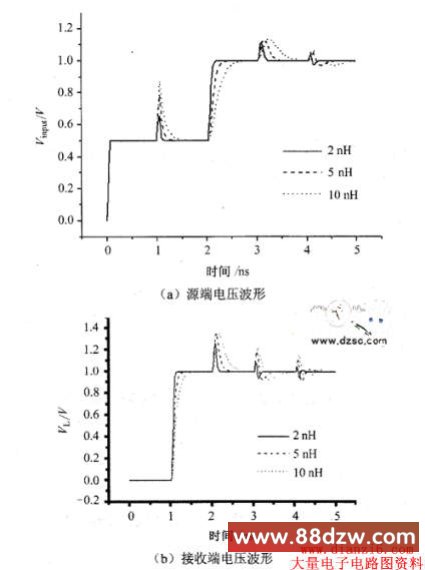

如果传输线末端开路,均匀传输线中途意外引入感性阻抗突变,路径时延TD1=TD1=0.5 ns,通过仿真可以看出电感值为2nH、5nH和10nH时源端和接收端电压波形如图3所示。

图2 末端电感不同时的接收端电压

图3 中途引入电感不同时的电压波形

在驱动端,1ns左右信号迅速上升超过50%然后又迅速下降,如果在近端有接收器,这种非单调性的波形变化可能会导致误触发。在接收端,信号出现过冲,而且上升沿有一个时延。随着电感的增大,过冲和时延越严重。

感性阻抗突变在电路中引起过冲甚至振铃,所以需控制信号回路中的电感量。当信号上升沿经过电感时,其瞬时阻抗为

根据经验,需要确保串联感抗低于传输线特性阻抗的⒛%,那么回路中允许串入的最大电感为

上面所有的分析只涉及简单的阻抗不连续情况下的反射,在实际系统中,信号从驱动端到远端的网络上可能会遇到各种非故意的阻抗突变,进而发生多次反射,手工计算相当复杂甚至无法完成。幸运的是,现在有很多SPICE电路仿真器和行为级仿真器可供使用。通过仿真预测阻抗突变对信号的影响,选择合适的设计方案是基于信号完整性PCB设计的一个重要方面。

- 上一篇:传输线上传播时串扰现象

《感性加载的反射》相关文章

编辑推荐

- ・ 什么是系统仿真

- ・ 什么是CPCI

- ・ 英特尔 Parallel Composer入门

- ・ 什么是支持数据库,什么是中宏数据库

- ・ 什么是数据交换技术

- ・ 什么是内部数据传输率

- ・ 什么是空间数据交换中心

- ・ 什么是差异备份

- ・ 什么是备份集

- ・ 什么是映像备份

- ・ IGBT模块

- ・ 什么是24脉波整流变压器

- ・ 自动变速器不能强制降挡故障原因、诊断与排

- ・ 什么是MD机

- ・ 中心频率,什么是中心频率

- ・ 功率单位mw和dbm的换算表

- ・ 中值滤波模块设计思路

- ・ 反馈振荡器的原理

- ・ 气体激光器简介

- ・ 数制与进位记数法

当前位置:

当前位置: