优化FPGA功耗的设计技术

[09-12 18:25:56] 来源:http://www.88dzw.com EDA/PLD 阅读:8764次

文章摘要:时钟FPGA的动态电源主要消耗在逻辑资源和互连结构等电容性元件的充放电活动。某个资源元件i的动态功耗可以利用下式建模:这里fi为开关频率, Ci为电容性负载,Vi为该资源的电压摆幅。充分考虑动态功率方程中的每一项,便可以降低功耗。例如,在时钟域可以决定设计的哪些部分需要快速时钟或较慢时钟。开关频率fi是动态功率方程的成分之一。由快速时钟驱动的逻辑相比由慢速时钟驱动的逻辑,开关更频繁。设计人员知道逻辑的哪些部分需要快速时钟,而哪些部分又可以运行在较慢速度之下,因此可以按照时钟所控制的功能予以划分,从而节省功率。一项设计的动态功耗还随布局布线而有很大变化。例如,如果两个相连的功能性实体彼此靠得很近

优化FPGA功耗的设计技术,标签:eda技术,eda技术实用教程,http://www.88dzw.com时钟

FPGA的动态电源主要消耗在逻辑资源和互连结构等电容性元件的充放电活动。某个资源元件i的动态功耗可以利用下式建模: 这里fi为开关频率, Ci为电容性负载,Vi为该资源的电压摆幅。充分考虑动态功率方程中的每一项,便可以降低功耗。例如,在时钟域可以决定设计的哪些部分需要快速时钟或较慢时钟。开关频率fi是动态功率方程的成分之一。由快速时钟驱动的逻辑相比由慢速时钟驱动的逻辑,开关更频繁。设计人员知道逻辑的哪些部分需要快速时钟,而哪些部分又可以运行在较慢速度之下,因此可以按照时钟所控制的功能予以划分,从而节省功率。

这里fi为开关频率, Ci为电容性负载,Vi为该资源的电压摆幅。充分考虑动态功率方程中的每一项,便可以降低功耗。例如,在时钟域可以决定设计的哪些部分需要快速时钟或较慢时钟。开关频率fi是动态功率方程的成分之一。由快速时钟驱动的逻辑相比由慢速时钟驱动的逻辑,开关更频繁。设计人员知道逻辑的哪些部分需要快速时钟,而哪些部分又可以运行在较慢速度之下,因此可以按照时钟所控制的功能予以划分,从而节省功率。

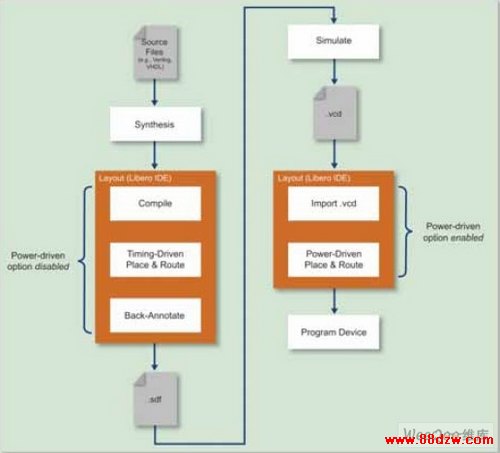

一项设计的动态功耗还随布局布线而有很大变化。例如,如果两个相连的功能性实体彼此靠得很近,两者间的布线长度可能缩短,因此会减小网络的电容性负载,致使功率降低。如今的FPGA开发软件通常支持功率驱动布线 (Power Driven Layout),可以自动实现这项功能,并能够降低25%或更多的总体动态功耗(实际数字取决于设计中的时钟和网络数目)。

架构改进

在架构层级上,通过对设计的时钟方案进行分析,来为时钟树寻求合适的时钟门控的方法是很有益的。如果设计已上电,但部分系统没有加载时钟,设计人员可以让时钟树不与设计的该部分连接,从而降低动态功耗。例如,如果一个时钟服务于一项必须功能和另一个非必须功能,设计人员则可执行一个逻辑信号,根据控制变量的状态,选择性地控制什么功能加载时钟,以及何时加载。不过,利用逻辑信号来实现时钟门控有可能导致时钟偏差(clock skew),必须予以管理。

另一个实现节能的方法是利用FPGA架构内部可用的所有节能模式,一般包括活动模式、待机模式,或睡眠模式。在活动模式下,FPGA会根据应用需求执行其预设功能,但在空闲时,则可进入待机或睡眠模式以节能。某些FPGA还能够切换到超低节能模式,关断空闲电路的时钟,同时保存器件状态。在该模式下,由于时钟关断,动态功耗不存在,静态功耗可忽略,这种技术一直用于ASIC器件,但最近开始出现在FPGA中。Actel的Flash*Freeze技术就是这种超低功耗模式示例。Flash*Freeze模式能够在1μs内进入和退出超低功耗模式,实际功耗低于2μW。手机就是利用多种节能模式的典型例子,它只在用户通话时才进入活动模式,其余时间均处于待机状态以节省能量,延长电池寿命。其它节能设计技术

选择性掉电(Selective power-down) 简单说是指关断芯片的某些部分或电路板上的某些芯片。为实现选择性关断,可采取多电源策略,割断某些模块的供电网络间的关联性。FPGA 架构中的掉电或睡眠模式还可用于空闲模块的选择性掉电。

宏模块优化(Macro optimization) 也能够节能,某些逻辑元件备有多种版本,分别针对高性能、高密度或低功耗而优化。高性能宏模块(high-performance macro)的功耗一般比其它版本更高,因此,仅在必须时才采用高性能宏模块,便可以实现节能。例如,快速加法器的功耗就大于较慢的逐位进位加法器。对二者间的差异进行分析,可以看出后者的动态功耗只有快速加法器的约十分之一。按照设计和目标功能所需的速度,低功耗选择可能完全足够。这适用于几乎所有类型的宏模块,包括乘法器、FIFO、RAM等。

分时复用(Time multiplexing)和最小I/O数设计划分二者是有助于I/O组开关的技术。尽量避免同时使用不同类型I/O技术,确保使用即适用,以及减小I/O驱动能力和压摆率,也行之有效。

图2:功率驱动布局布线设计流程

动态电压调节 (Dynamic voltage scaling) 是另一种节能设计技术,由于功率大小与电压的平方成正比,意味着降低电源电压即可显著影响功效。如果系统要求的性能高于低压I/O所能提供的,则可以在非关键性能引脚上使用低压I/O,并在关键信号引脚上使用较高电压I/O,以提供出色的替代方案。目前,市场上某些低功耗FPGA完全可以由单个1.2 v电源为内核和I/O供电。Actel的 IGLOO 和 nano器件就是例子。

《优化FPGA功耗的设计技术》相关文章

- › 优化FPGA功耗的设计技术

- 在百度中搜索相关文章:优化FPGA功耗的设计技术

- 在谷歌中搜索相关文章:优化FPGA功耗的设计技术

- 在soso中搜索相关文章:优化FPGA功耗的设计技术

- 在搜狗中搜索相关文章:优化FPGA功耗的设计技术

当前位置:

当前位置: