利用串行RapidIO实现FPGA协处理

[09-12 18:26:20] 来源:http://www.88dzw.com EDA/PLD 阅读:8524次

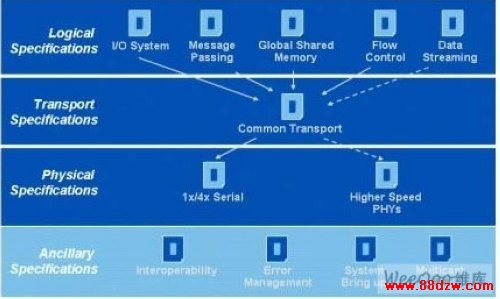

文章摘要:图4:SRIO规范平台中的运算资源有了可配置的处理资源,开发人员就可以用硬件实现他们的应用,例如数据压缩和加密算法甚至过去只在软件中实现的整套防火墙和保密应用,如今都可以在硬件上实现但这样做需要具备共享带宽和强大处理能力的大型并行生态系统,也就是说,要求利用CPU、NPU、FPGA和/或ASIC进行共享式或分布式处理构建此类系统时,对运算资源的一些要求包括:1. 支持复杂拓扑的分布式处理能力;2. 高度可靠的直接对等通信能力;3. 多个异构操作系统;4. 通过多个异构操作系统支持通信数据层;5. 具有广泛生态系统支持的模块化和可扩展平台SRIO协议规范和架构支持嵌入式和无线基础设施领域中运算设

利用串行RapidIO实现FPGA协处理,标签:eda技术,eda技术实用教程,http://www.88dzw.com

图4:SRIO规范

平台中的运算资源

有了可配置的处理资源,开发人员就可以用硬件实现他们的应用,例如数据压缩和加密算法甚至过去只在软件中实现的整套防火墙和保密应用,如今都可以在硬件上实现但这样做需要具备共享带宽和强大处理能力的大型并行生态系统,也就是说,要求利用CPU、NPU、FPGA和/或ASIC进行共享式或分布式处理构建此类系统时,对运算资源的一些要求包括:

1. 支持复杂拓扑的分布式处理能力;

2. 高度可靠的直接对等通信能力;

3. 多个异构操作系统;

4. 通过多个异构操作系统支持通信数据层;

5. 具有广泛生态系统支持的模块化和可扩展平台

SRIO协议规范和架构支持嵌入式和无线基础设施领域中运算设备的不同要求有了SRIO,就可以实现系统结构的独立性,部署达到运营商级可靠度、具备高级流量管理功能,并具有高性能和高吞吐量的可扩展系统此外,广泛的供应商生态系统也更方便设计师采用现货元件构造SRIO系统SRIO是一种基于分组的协议,它支持:

1. 采用分组操作(包括读、写和消息传递)实现数据搬移;

2. I/O非一致性功能和缓存一致性功能;

3. 通过支持数据流传送和SAR功能实现高效的互通和协议封装;

4. 通过支持数百万条数据流、256种流量类别和有损操作实现一种流量管理架构;

5. 支持多事务请求流(包括配置QoS)的流量控制;

6. 为减少带宽分配、事务预定和死锁避免等问题而支持优先级划分;

7. 通过系统发现、配置和学习实现对标准拓扑(树型和网格型)和任意拓扑(菊链)等多种硬件拓扑方式的支持,包括支持多个主机;

8. 错误管理和分类(可恢复、通知和严重)

串行RapidIO的IP方案

为了在通过逻辑(I/O)和传输层IP上的目标接口和源接口收发用户数据时支持完全兼容的最大载荷操作,Xilinx等厂商根据最新的RapidIO v1.3规范设计了其端点IP解决方案。

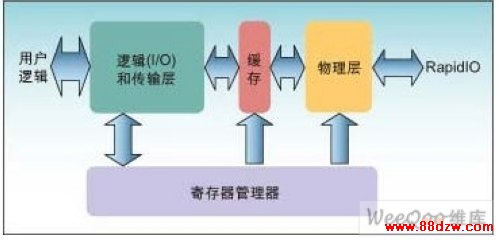

图5所示是Xilinx的一套完整的SRIO端点IP方案,它包含以下组成部分:

1. LogiCORE RapidIO 逻辑 (I/O)和传输层IP;

2. 缓冲层参考设计;

3. LogiCORE串行RapidIO物理层IP;

4. 寄存器管理器参考设计

图5:Xilinx的 SRIO端点IP架构

IP架构

Xilinx提供了缓冲层参考设计的源代码,该设计可完成分组的自动排队和优先级重新划分SRIO物理层IP可以实现链路训练和初始化、发现和管理以及错误与重试恢复机制此外,在该物理层IP中还对高速收发器进行了实例化,以便支持线速为1.25Gbps、2.5Gbps和3.125Gbps 的1通道和4通道SRIO总线连接。

该方案中提供的寄存器管理器参考设计允许SRIO主设备对端点设备配置、链路状态、控制和超时机制进行配置和维护另外,该寄存器管理器还提供了可让用户设计探测端点设备状态的端口。

LogiCORE则提供了完整的端点IP该IP已通过业界领先SRIO器件厂商的测试用户可通过Xilinx CoreGen GUI工具获得LogiCORECoreGen工具可以帮助用户配置波特率和端点LogiCORE支持流量控制、重传抑制、门铃和消息传递等扩展特性因此,用户可以创建一套专门针对应用需求优化了的灵活、可调整和定制化的SRIO端点IP。

利用Xilinx和其他厂商提供的大多数高性能FPGA中的各种资源,系统设计师就能轻松创建并部署其智能方案,以增强产品在上市时间、可调整性、可扩展性、适应未来发展等各方面的优势下面给出了一些采用SRIO和DSP技术的系统设计实例。

SRIO系统应用实例

1.嵌入式系统

《利用串行RapidIO实现FPGA协处理》相关文章

- › 利用串行RapidIO实现FPGA协处理

- 在百度中搜索相关文章:利用串行RapidIO实现FPGA协处理

- 在谷歌中搜索相关文章:利用串行RapidIO实现FPGA协处理

- 在soso中搜索相关文章:利用串行RapidIO实现FPGA协处理

- 在搜狗中搜索相关文章:利用串行RapidIO实现FPGA协处理

当前位置:

当前位置: