基于FPGA的提取位同步时钟DPLL设计

[09-12 18:26:49] 来源:http://www.88dzw.com EDA/PLD 阅读:8354次

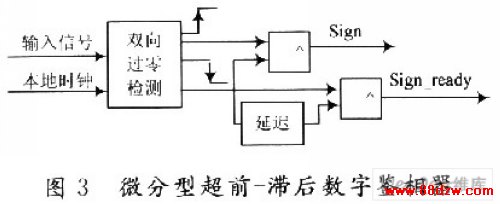

文章摘要:微分型超前一滞后数字鉴相器的原理图如图3所示。2.2 数字滤波器结构及其买现方法在数字锁相环路中,环路滤波器通常使用数字滤波器,它们与模拟锁相环路中的模拟环路滤波器相对应。数字环路滤波器在环路中对输入噪声起抑制作用,并且对环路的校正速度起调节作用。由于采用微分型超前一滞后型数字鉴相器,随机噪声会引起DPD的相位抖动,会生成影响DCO动作的控制脉冲,所以对于DPD输出的Sign和Sign_ready不能作为直接驱动指导后面DCO的控制信号,DPD的滤波功能是通过一个Mod为8的计数器来实现的。当Sign_ready为1时,DPD的Mod开始加减计数(Mod复位后为8),计数的方向由Sign来控制

基于FPGA的提取位同步时钟DPLL设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com 微分型超前一滞后数字鉴相器的原理图如图3所示。

2.2 数字滤波器结构及其买现方法

在数字锁相环路中,环路滤波器通常使用数字滤波器,它们与模拟锁相环路中的模拟环路滤波器相对应。数字环路滤波器在环路中对输入噪声起抑制作用,并且对环路的校正速度起调节作用。

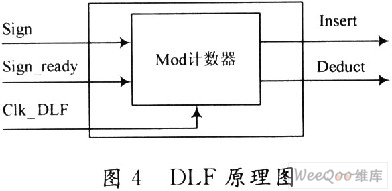

由于采用微分型超前一滞后型数字鉴相器,随机噪声会引起DPD的相位抖动,会生成影响DCO动作的控制脉冲,所以对于DPD输出的Sign和Sign_ready不能作为直接驱动指导后面DCO的控制信号,DPD的滤波功能是通过一个Mod为8的计数器来实现的。当Sign_ready为1时,DPD的Mod开始加减计数(Mod复位后为8),计数的方向由Sign来控制。当Sign为1时,表示本地时钟超前于输入信号,Mod做加法计数,逐次加法直到15,进位变为8,Inset输出一个1μs的高电平;同样,当Sign为0时,表示本地时钟超前于输入信号,Mod做减法计数,逐次加法直到1,借位变为8,Deduct输出一个1μs的高电平。DLF原理图如图4所示。

由于噪声和抖动一般是无序的,除非噪声在同一方向出现8次,滤波器才会输出误动作。另外Clk_DLF是Clk_DPD的两倍频率,有助于提高滤波精度。

2.3 振荡器结构及其实现方法

数控振荡器,又称为数字钟,它在数字锁相环路中所处的地位相当于模拟锁相环中的电压控制振荡器。它的输出是一个脉冲序列,而该输出脉冲序列的周期受数字环路滤波器产生的校正信号所控制。本次设计主要采用加、扣脉冲式DCO,该振荡器的特点是每一个鉴相周期输出本地估算信号是超前或者滞后于输入信号的信息,经滤波器处理后输出加或扣脉冲信号,以此控制DCO的输出相位。

DCO根据DLF输出的Insert和Deduct来调节本地时钟,输出与曼彻斯*位信号同相同频的时钟。另外,DPD和DLF的工作时钟也由DCO产生(Clk_DPD和Clk_DLF同相,前者是后者频率的1/2),构成了DPLL系统闭环。DCO原理图如图5所示。一般DCO分为三个工作模块,即高速振荡器、相位调节器和分频器。由于本次设计的特殊性,将DCO划分为两个工作模块,即将相位调节器和分频器合并,由DLF产生的Insert和Deduct来指导相位调节,并输出系统要求的位信号时钟。

相位调节与分频输出如图6所示。

由于之前的DLF的Mod为8,而Clk_DLF的频率是500 kHz,周期即2μs,所以每次调节的相位最小单位为120 ns,20 ns×(5+1)=120ns。DLF在同一方向上接到DPD的Sign信号4次后动作,由于本次项目做曼彻斯特解码时,前导码是32个,换算成位信号有64个,由于曼彻斯*是10交替的,故输入信号的有效跳变是32次。经过多次仿真和实验,DPLL一般在前25个前导码内即可稳定,稳定后在120 ns的范围内跳动。

3 锁相环路建模及分析

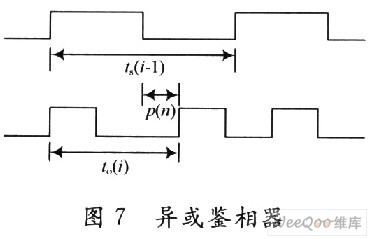

定义如下变量:ts为外加信号周期;to为反馈信号周期;p(n)为输出信号和外加信号的相位差。当输出信号和外加信号的相位差小于π时,鉴相特性是线性的,如图7所示。

《基于FPGA的提取位同步时钟DPLL设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的提取位同步时钟DPLL设计

- 在谷歌中搜索相关文章:基于FPGA的提取位同步时钟DPLL设计

- 在soso中搜索相关文章:基于FPGA的提取位同步时钟DPLL设计

- 在搜狗中搜索相关文章:基于FPGA的提取位同步时钟DPLL设计

当前位置:

当前位置: