FPGA的时钟频率同步设计

[09-12 18:26:53] 来源:http://www.88dzw.com EDA/PLD 阅读:8417次

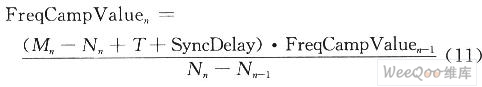

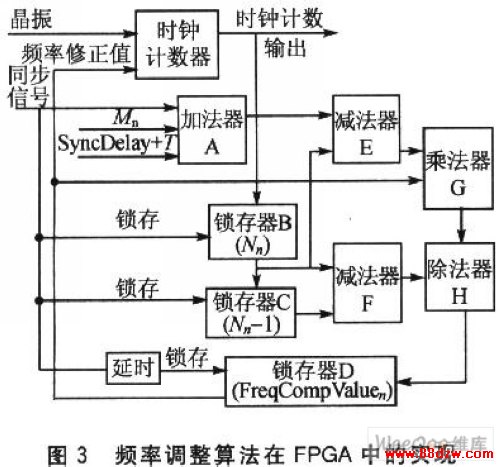

文章摘要:FreqCompValuen=kn・FreqCompValuen-1 (10)3 频率补偿算法在FPGA中的实现由式(4)和式(10)可得:频率补偿就是在每个同步周期计算FreqCompValuen,FPGA提供了参数化的乘法器兆函数(1pm_mult)和除法器兆函数(1pm_divide),可以快速实现上述算法。原理如图3所示,在每个同步周期同步信号的驱使下,锁存器B和C分别锁存当前时钟读数和上个同步周期时钟读数,同时将主时钟读数输入到加法器A中,经过减法器E、F和乘法器G,以及除法器H后计算出新的FreqCompValuen,并在同步信号的驱动下,将其锁存到锁存器D中。由于中间的计算结果要

FPGA的时钟频率同步设计,标签:eda技术,eda技术实用教程,http://www.88dzw.comFreqCompValuen=kn・FreqCompValuen-1 (10)

3 频率补偿算法在FPGA中的实现

由式(4)和式(10)可得:

频率补偿就是在每个同步周期计算FreqCompValuen,FPGA提供了参数化的乘法器兆函数(1pm_mult)和除法器兆函数(1pm_divide),可以快速实现上述算法。原理如图3所示,在每个同步周期同步信号的驱使下,锁存器B和C分别锁存当前时钟读数和上个同步周期时钟读数,同时将主时钟读数输入到加法器A中,经过减法器E、F和乘法器G,以及除法器H后计算出新的FreqCompValuen,并在同步信号的驱动下,将其锁存到锁存器D中。由于中间的计算结果要经过一定的时钟周期,所以锁存器D的锁存信号要延时一定的晶振周期。在本设计中延时50个FreqOsc,即在<1μs的情况下就可以得到新的频率补偿值。

同步报文的传输延迟SyncDelay理论上是不变的,而实际上报文在传输过程中有抖动。参考文献[3]对此进行了分析,并指出同步周期越长,报文传输延迟抖动的影响就越小,因此可以忽略不计。

4 实验验证

主时钟采用50 MHz的有源晶振来实现,并将其作为固定时钟;从时钟采用30 MHz有源晶振,通过FPGA的锁相环PLL将其频率倍频到60 MHz,然后1.2分频,实现可调频率的50 MHz时钟。

让主时钟和从时钟以一定的时间间隔产生中断,并通过逻辑分析仪采样中断信号分析其偏差。由于系统时钟的分辨率为20 ns,采用广州致远电子有限公司的逻辑分析仪LA1532,其最大采样频率为100 MHz,所以偏差测量精度可以达到10 ns。图4(a)是未进行同步前两个时钟的偏差分析,X轴表示主时钟和从时钟的计时长度,Y轴表示主时钟和从时钟的计时偏差。从图中可以看出两个时钟的偏差大概为5×10-6,即1 s内的偏差可以达到5μs。图4(b)为同步后主时钟和从时钟偏差测量结果,共测量1 000次,其10 ms内同步偏差在±20 ns。X轴表示测量时间,Y轴表示主从时钟同步偏差。图4(c)为同步后两个从时钟偏差测量结果,共测量1 000次,其10 ms内同步偏差在±40 ns。X轴表示测量时间,Y轴表示从时钟之间同步偏差。

结 语

基于时钟频率调整的时间同步方法,实现简单,而且没有复杂的软件同步协议,占用较小的网络带宽就可以实现高精度的时钟同步,在硬件上只需要低成本的FPGA支持。

《FPGA的时钟频率同步设计》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA的时钟频率同步设计

- 在谷歌中搜索相关文章:FPGA的时钟频率同步设计

- 在soso中搜索相关文章:FPGA的时钟频率同步设计

- 在搜狗中搜索相关文章:FPGA的时钟频率同步设计

当前位置:

当前位置: