雷达视频积累算法在FPGA上的实现

[09-12 18:27:30] 来源:http://www.88dzw.com EDA/PLD 阅读:8263次

文章摘要:图3中的clk为系统主时钟;count_dist为距离计数器;acc_en为视频积累的使能信号,acc_en为高电平时有效;count_dist,clk与acc_en为控制时序关系的主要系统变量;acc_data为求模后输入的非相参信号,系统的视频信号实时不断地输入到FPGA中。FPGA通过时序控制将acc_data信号量化后为RAM_data信号;当RAM的读信号RAM_we为高电平时,RAM_data写入SRAM地址中,通过时序控制将前面L-1个周期的量化信号存储在高速SRAM中,待信号在SRAM中存满后,即RAM_rd为高电平;RAM_we为低电平时,通过时序控制,将存入SRAM中的同一

雷达视频积累算法在FPGA上的实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com图3中的clk为系统主时钟;count_dist为距离计数器;acc_en为视频积累的使能信号,acc_en为高电平时有效;count_dist,clk与acc_en为控制时序关系的主要系统变量;acc_data为求模后输入的非相参信号,系统的视频信号实时不断地输入到FPGA中。

FPGA通过时序控制将acc_data信号量化后为RAM_data信号;当RAM的读信号RAM_we为高电平时,RAM_data写入SRAM地址中,通过时序控制将前面L-1个周期的量化信号存储在高速SRAM中,待信号在SRAM中存满后,即RAM_rd为高电平;RAM_we为低电平时,通过时序控制,将存入SRAM中的同一距离单元上的前L-1个信号读出,并与当前输入信号在FPGA中进行累加完成窗孔长度为L的小滑窗检测,从而实现对非相参视频信号的视频积累。

4 仿真验证

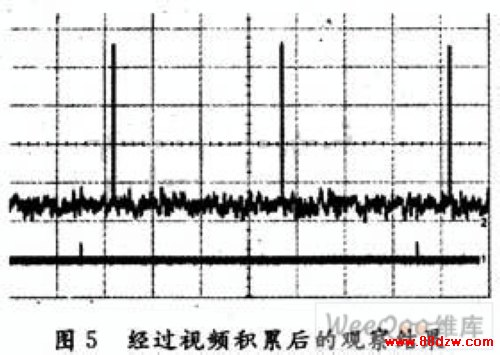

为了验证本文原理以及本系统的实现效果,首先模拟产生雷达信号处理中经过求模以后的相参视频信号,该信号仅含有幅度信息和杂波(根据参数设置直接在FPGA芯片中利用软件编程产生),对该模拟信号进行视频积累,经D/A变换送给示波器显示。将编译综合后的BIT文件下载到FPGA芯片中进行系统联调,最后在示波器上查看仿真的结果。图4为经过求模后的雷达相参视频信号在示波器上的截图,该信号的杂波为近似服从均值为0的均匀分布;图5为对该模拟信号进行视频积累后在示波器上的截图。

从仿真的结果可以看出,利用本系统对经过求模后的信号进行视频积累取得了比较理想的效果。

5 结语

本文着重介绍了利用FPGA芯片实现视频积累的原理和过程。利用FPGA进行雷达视频积累,可使系统具有更大的灵活性,减少了系统的体积,提高了系统的可靠性,大大缩短了系统开发的周期。随着FPGA芯片以及设计更新软件的更新与快速发展,FPGA芯片将具有更高速的重复复杂计算的能力,同时又具有软件的灵活性,并可以重复利用硬件来降低成本,模糊了硬件与软件之间的界限,使硬件系统具有更大的灵活性以及通用性。

本文最后利用FPGA软件编程模拟实现了一个经过求模后的雷达相参视频信号,并利用本系统对该信号进行了视频积累,取得了较好的效果。

《雷达视频积累算法在FPGA上的实现》相关文章

- › 雷达视频积累算法在FPGA上的实现

- 在百度中搜索相关文章:雷达视频积累算法在FPGA上的实现

- 在谷歌中搜索相关文章:雷达视频积累算法在FPGA上的实现

- 在soso中搜索相关文章:雷达视频积累算法在FPGA上的实现

- 在搜狗中搜索相关文章:雷达视频积累算法在FPGA上的实现

当前位置:

当前位置: