基于FPGA实现的FFT插值正弦波频率估计

[09-12 18:28:24] 来源:http://www.88dzw.com EDA/PLD 阅读:8842次

文章摘要:2 算法硬件实现本文算法充分利用了FPGA并行计算的优点,在FPGA实现时采用流水线模式,经过固有时间后,每个时钟周期可以输出一个指定操作的结果,提高了算法的运算速度。从前面的分析可知,整个测频算法主要包括粗测频和精测频2个部分:首先对信号作FFT运算并进行谱峰搜索得到峰值位置;再通过插值FFT运算得到频率偏差δ1,δ2;粗测频部分可以直接调用相关FPGA的FFT库函数完成。从式(3)可知精测频部分需要大量计算三角函数,本文采用查表法来实现。整个算法流程如图2所示。3 仿真分析信噪比定义为:,σ为噪声均方误差。对正弦波信号,在相位、幅度和频率3个参数均是未知的情况下,频率估计的方差下限为:式中

基于FPGA实现的FFT插值正弦波频率估计,标签:eda技术,eda技术实用教程,http://www.88dzw.com2 算法硬件实现

本文算法充分利用了FPGA并行计算的优点,在FPGA实现时采用流水线模式,经过固有时间后,每个时钟周期可以输出一个指定操作的结果,提高了算法的运算速度。

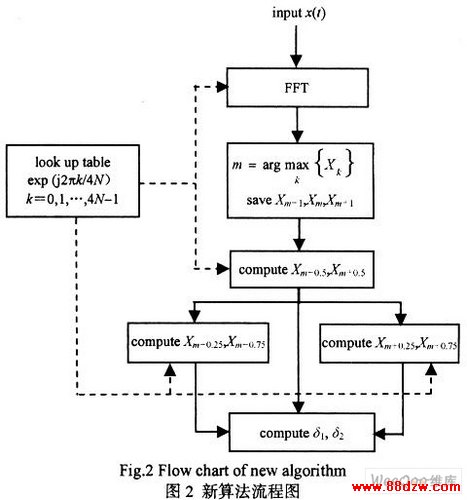

从前面的分析可知,整个测频算法主要包括粗测频和精测频2个部分:首先对信号作FFT运算并进行谱峰搜索得到峰值位置;再通过插值FFT运算得到频率偏差δ1,δ2;粗测频部分可以直接调用相关FPGA的FFT库函数完成。从式(3)可知精测频部分需要大量计算三角函数,本文采用查表法来实现。整个算法流程如图2所示。

3 仿真分析

信噪比定义为:,σ为噪声均方误差。对正弦波信号,在相位、幅度和频率3个参数均是未知的情况下,频率估计的方差下限为:

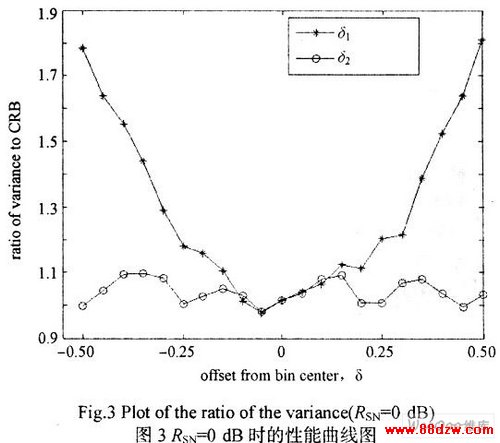

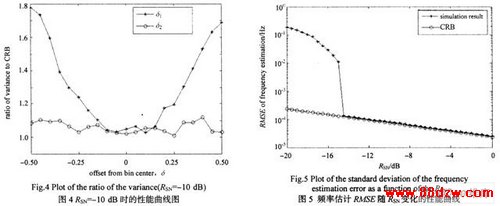

式中N为样本数。在仿真中设fs=167 MHz,N=512,因此两条谱线间的频率差为△f=fs/N。现取fi=45.5△f+(i-1)△f/20(i=l,2,…,21)的正弦波,即对应FFT后峰值位置与信号真实峰值偏差δ为[-0.5,0.5]。对每个频率fi的取值分别作l 000次Monte Carlo试验,计算δl,δ2的均方根误差(RMSE),定义比率R=RMSE/CRB,仿真结果如图3、图4所示。RSN取-20 dB~0 dB,步长为0.5 dB,分别做1 000次Monte Carlo试验,计算新算法的归一化频率估计均方误差,仿真结果如图5所示。

仿真结果表明δ2不随被估计信号的频率分布而产生波动;当RSN>-14 dB时,新算法频率估计值的方差在整个频段都接近卡拉美-罗限,具有稳定的性能。

4 结论

本文在分析Rife,MRife和傅里叶系数插值迭代3种算法的基础上,将串行迭代变为并行迭代,由此得出了一种快速频率估计算法,并分析了新算法与前3种算法的异同。计算机仿真结果证实新算法能够快速、高精度估计单频信号的频率,便于工程实现,适合应用在雷达、电子对抗等对处理实时性要求非常高的领域。(现代电子技术 作者:江 舸,陶荣辉,李 钒,李合生 中国工程物理研究院)

《基于FPGA实现的FFT插值正弦波频率估计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA实现的FFT插值正弦波频率估计

- 在谷歌中搜索相关文章:基于FPGA实现的FFT插值正弦波频率估计

- 在soso中搜索相关文章:基于FPGA实现的FFT插值正弦波频率估计

- 在搜狗中搜索相关文章:基于FPGA实现的FFT插值正弦波频率估计

当前位置:

当前位置: