基于VerilogHDL的背景噪声扣除电路设计

[09-12 18:29:00] 来源:http://www.88dzw.com EDA/PLD 阅读:8679次

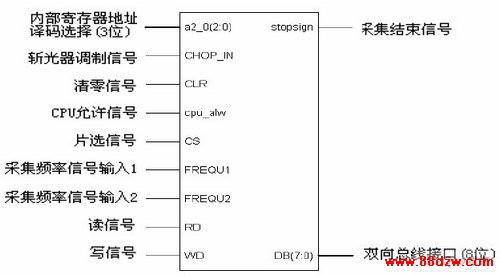

文章摘要:主模块的外部接口如图3所示。FREQU1, FREQU2为采样频率输入1和2;CHOP_IN斩光器或调制频率输入,CLR为清零信号,高电平有效;cpu_alw为MCU发出的允许信号,高电平有效;stopsign是采集完成信号,高电平为完成;WD,RD,CS为是写、读、片选信号;DB为8位双向数据总线;a2_0为3线片内寄存器地址译码选择接口。图3 背景噪声扣除主模块综合生成原理图的外部接口16位二进制加减计数模块(bit16addsub)是背景扣除电路的具体实现单元,代码如下所示。module bit16addsub(input wire FREQU,//采样频率输入input wire CH

基于VerilogHDL的背景噪声扣除电路设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com 主模块的外部接口如图3所示。FREQU1, FREQU2为采样频率输入1和2;CHOP_IN斩光器或调制频率输入,CLR为清零信号,高电平有效;cpu_alw为MCU发出的允许信号,高电平有效;stopsign是采集完成信号,高电平为完成;WD,RD,CS为是写、读、片选信号;DB为8位双向数据总线;a2_0为3线片内寄存器地址译码选择接口。

图3 背景噪声扣除主模块综合生成原理图的外部接口

16位二进制加减计数模块(bit16addsub)是背景扣除电路的具体实现单元,代码如下所示。

module bit16addsub(

input wire FREQU,//采样频率输入

input wire CHOP_IN,//斩光器输入

input EN,//启停控制

input wire CLR,//请零

input wire [15:0] STA_NUM,//初始数值

output reg[15:0] result_num //计数结果输出

);

always @(posedge FREQU or posedge CLR)//对采集信号和清零信号敏感

begin

if(CLR==1)//清零

result_num<=STA_NUM;//重新读入预置数

else if(EN==1&&CHOP_IN==1&&FREQU==1)

result_num<=result_num+1;//在使能的状态下调制的信号高电平时加计数

else if(CHOP_IN==0&&EN==1&&FREQU==1)

result_num<=result_num-1;//在使能的状态下调制信号的低电平时减计数

end

endmodule

采集控制模块(Ctrol)是整个设计的时序控制核心,它输出的ctrol与16位二进制加减计数模块(bit16addsub)的EN向连接便可实现自动控制计数的启动,待计数周期溢出时停止,计数完成后由stopsign后给出高电平信号通知MCU。其完整代码如下:

module Ctrol(input wire reset, //复位信号

input wire cpu_alw, //MCU允许信号

input wire chop_in, //斩光器输入计数

input wire [16:0] status_in, //计数周期数值

output reg ctrol, //加减计数器的启停控制信号

output reg stopsign //计数完成信号

);

reg [16:0]num_count;//内部计数周期寄存器

always @(posedge reset or posedge chop_in)

begin

if(reset)//复位

begin

num_count<=status_in; //读入计数周期

ctrol<=0; //停止计数

stopsign<=0; //没有完成计数

end

else if(chop_in==1&&cpu_alw==1)//允许计数

begin

if(num_count>0) //采集未完成

begin

ctrol<=1; //16加减计数器使能

num_count<=num_count-1;//计数周期减一

end

else

begin

ctrol<=0; //计数停止

stopsign<=1; //通知MCU

end

end

end

endmodule

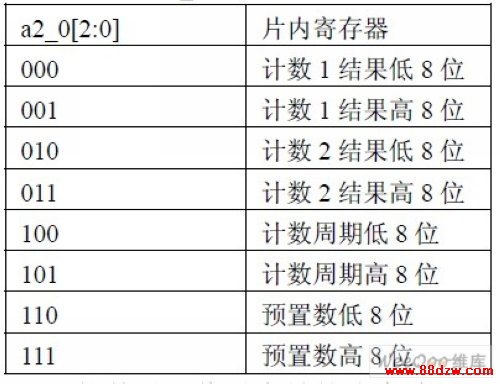

读写接口模块(Addselec)在编程时采用通用的双向数据总线输入输出方法,经过a2_0的3线译码选择寄存器地址,可对计数周期和预置数进行赋值,并可读出最后计数结果。表1给出了译码对应的寄存器地址。

表1 a2_0译码选择真值表

《基于VerilogHDL的背景噪声扣除电路设计》相关文章

- › 基于Verilog HDL的UART模块设计与仿真

- › 基于VerilogHDL的背景噪声扣除电路设计

- 在百度中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在谷歌中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在soso中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

- 在搜狗中搜索相关文章:基于VerilogHDL的背景噪声扣除电路设计

当前位置:

当前位置: