基于ARM+FPGA的重构控制器设计

[09-12 18:29:14] 来源:http://www.88dzw.com EDA/PLD 阅读:8767次

文章摘要:3.2重构控制器工作原理ARM执行的初始化工作包括程序更新加载运行,FPGA参数设定等;FPGA设定内部寄存器和逻辑状态的初始值、内部缓冲区数据清零等。重构控制器示意图如图4所示。图中ARM处理器一方面通过ARM总线读取外部FLASH中的配置方案,对其进行并串转化操作,将其存储到FLASH存储器中;另一方面重构控制器中模拟TAP控制器的FPGA,从ARM内置的FLASH存储器中读取配置文件,并执行ARM处理器发出的指令解译该文件,重构控制器解释二进制文件方法如下:在ARM处理器的控制下,从装载配置文件的FLASH中读出一个字节,判断是哪条JTAG指令,然后根据指令的格式作具体的处理,产生TCK

基于ARM+FPGA的重构控制器设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com3.2重构控制器工作原理

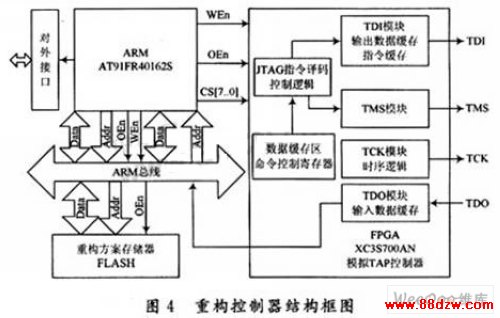

ARM执行的初始化工作包括程序更新加载运行,FPGA参数设定等;FPGA设定内部寄存器和逻辑状态的初始值、内部缓冲区数据清零等。

重构控制器示意图如图4所示。图中ARM处理器一方面通过ARM总线读取外部FLASH中的配置方案,对其进行并串转化操作,将其存储到FLASH存储器中;另一方面重构控制器中模拟TAP控制器的FPGA,从ARM内置的FLASH存储器中读取配置文件,并执行ARM处理器发出的指令解译该文件,重构控制器解释二进制文件方法如下:在ARM处理器的控制下,从装载配置文件的FLASH中读出一个字节,判断是哪条JTAG指令,然后根据指令的格式作具体的处理,产生TCK,TMS,TDI和TDO信号,作为目标可编程器件的JTAG接口激励,与目标可编程器件的JTAG口串联成菊花链,在ARM处理器的控制下,对目标可编程器件进行在系统编程。被重构的FPGA由支持局部动态重构的Xilinx公司的Virtex-4系列FPGA来实现。

4 结 语

本文介绍的重构控制器既具有ARM微控制器所拥有的高速处理器核、体积小、集成度高、运算速度快、存储器容量大、功耗低等特点,又具有FPGA强大的并行计算能力和方便灵活的动态可重构性,使硬件信息(可编程器件的配置信息)像软件程序一样被动态调用或修改。对于特定的目标FPGA芯片,在一定控制逻辑的驱动下,对芯片的全部或部分逻辑资源重新进行动态配置,从而实现硬件的时分复用,灵活快速地改变系统功能,节省逻辑资源,满足大规模应用需求。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《基于ARM+FPGA的重构控制器设计》相关文章

- › 基于ARM+FPGA的重构控制器设计

- › 基于ARM的FPGA加载配置实现

- › 基于ARM7+μC/OSII的数据采集系统设计

- › 基于ARM的信号发生器人机交互系统设计

- › 基于ARM嵌入式系统的ISP设计

- › 基于ARM微处理器的uC/OS的移植设计

- 在百度中搜索相关文章:基于ARM+FPGA的重构控制器设计

- 在谷歌中搜索相关文章:基于ARM+FPGA的重构控制器设计

- 在soso中搜索相关文章:基于ARM+FPGA的重构控制器设计

- 在搜狗中搜索相关文章:基于ARM+FPGA的重构控制器设计

分类导航

最新更新

当前位置:

当前位置: