FPGA设计开发中应用仿真技术解决故障的方法

[09-12 18:29:31] 来源:http://www.88dzw.com EDA/PLD 阅读:8265次

文章摘要:Quartus II 平台用SignalTap抓到信号的界面如图2所示。图2 SignalTap抓信号界面在信号名称上单击右键,选择图2所示Create SignalTap II List File选项,生成如图3格式界面。图3 SignalTap II List File界面图3中界面上半部分显示的是list对信号个数及信号名的描述,下半部分是采样点所对应的信号值,带h的表示是十六进制数值。将list file另存为文本格式文件即可,如图4所示。图4 “另存为”选项界面此后可以把这个文本文件中无用的描述删掉,只留SignalTap抓出来的数据(空格、h等符号也要删掉),另存为.dat文件供仿

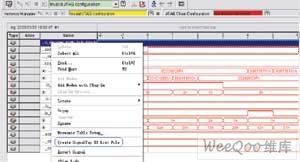

FPGA设计开发中应用仿真技术解决故障的方法,标签:eda技术,eda技术实用教程,http://www.88dzw.com Quartus II 平台用SignalTap抓到信号的界面如图2所示。

图2 SignalTap抓信号界面

在信号名称上单击右键,选择图2所示Create SignalTap II List File选项,生成如图3格式界面。

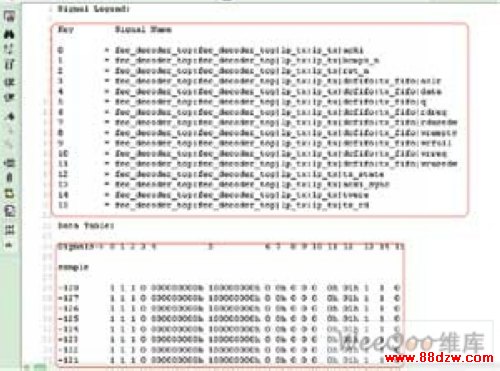

图3 SignalTap II List File界面

图3中界面上半部分显示的是list对信号个数及信号名的描述,下半部分是采样点所对应的信号值,带h的表示是十六进制数值。

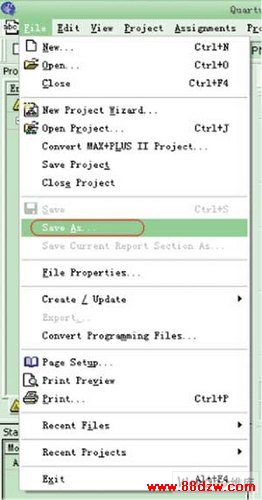

将list file另存为文本格式文件即可,如图4所示。

图4 “另存为”选项界面

此后可以把这个文本文件中无用的描述删掉,只留SignalTap抓出来的数据(空格、h等符号也要删掉),另存为.dat文件供仿真使用。

有了故障出现时的输入数据,我们就可以在仿真环境下构建故障出现的条件。

②利用.dat文件建立bug出现的条件

用verilog语言编写仿真文件(testbench),使用语句$readmemh或$readmemb将.dat文件中的数据存储到一个设定的ram中,如:$readmemh(“s.dat”,ram)。

注意$readmemh读取是按照十六进制数据进行(认为.dat文件中的数据都是十六进制数),会自动将其转换为4位二进制数存入ram中,所以设定的ram位宽要是.dat文件中数据位宽的4倍;使用$readmemb时,存储SignalTap所抓信号时,信号都要先设定为binary类型,ram位宽就是.dat文件数据的位宽。ram的深度为.dat文件中数据的个数。

然后在程序里把ram中数据按照所对应时钟沿输出到一个寄存器变量中,ram地址累加即可。

always@(posedge clk)

begin

data<=ram[addr];

addr<=addr+1'b1;

end

复现bug存在条件时,需将模块的输入信号与ram中的数据位相对应,仿真文件调用模块时,将寄存器data对应位作为输入接入即可。

在仿真环境中复现bug波形如图5所示。

图5 modelsim环境下复现的出错数据

把图5和图1进行比较,可见通过这种方法我们在仿真环境下建立了bug出错时的环境,得到相同的输出出错数据。

③修改程序后在仿真环境验证修改是否成功

修改程序后,我们只要使用同样的环境进行仿真,并且有针对性的观察bug是否解决。本例中出现bug的原因是使用了异步FIFO,改成同步FIFO后,问题应该就会解决,我们可以通过仿真验证。修改程序后仿真的波形如图6所示。

图6 修改程序后相同条件下的输出数据

由图6可见,修改后相同的条件FIFO读出4个数,说明没有读空,符合要求,bug解决。图7为版本编译后上板使用SignalTap抓取的信号波形,以作比较。

图7 修改程序后SignalTap抓的信号

比较后易见,波形完全相同,说明方法可行。

总结

文中描述的方法可针对各种的故障的解决。在故障出现时,只需定位出错的模块,这些模块内嵌一些子模块也无妨;抓信号时将故障模块的输入输出信号抓出即可;利用输入信号重建故障环境,若仿真输出信号和所抓输出信号相同,说明故障环境建立正确;用这个仿真平台就可以具体定位是哪个子模块、哪个信号出错,而不需要在SignalTap中把这些信号抓出来;并且在修改代码后可以验证是否修改成功,节省时间,很明确的证明故障真的被解决了,事半功倍。

- 上一篇:FPGA高速收发器设计原则

《FPGA设计开发中应用仿真技术解决故障的方法》相关文章

- › 高性能FPGA中的高速SERDES接口

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › FPGA在平板显示器中的应用

- › FPGA与DS18B20型温度传感器通信的实现

- 在百度中搜索相关文章:FPGA设计开发中应用仿真技术解决故障的方法

- 在谷歌中搜索相关文章:FPGA设计开发中应用仿真技术解决故障的方法

- 在soso中搜索相关文章:FPGA设计开发中应用仿真技术解决故障的方法

- 在搜狗中搜索相关文章:FPGA设计开发中应用仿真技术解决故障的方法

当前位置:

当前位置: