基于FPGA的工控领域监控系统设计

[09-12 18:30:21] 来源:http://www.88dzw.com EDA/PLD 阅读:8657次

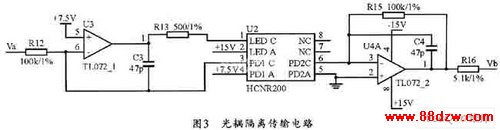

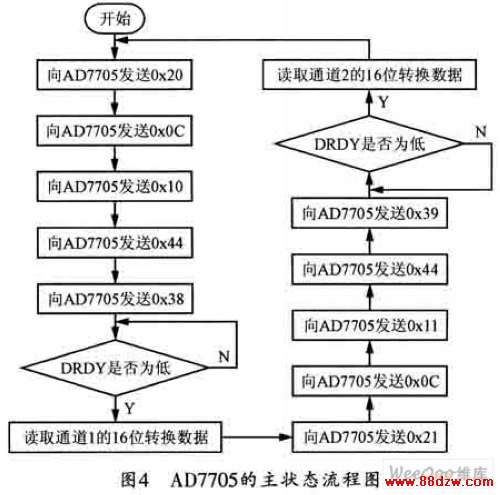

文章摘要:图3所示为光耦隔离传输电路,由图2所示的差分放大电路输出的电压信号Va经过光耦隔离电路后,即可以l:1的形式传送,即Vb点的电压信号和差分放大后的信号Va是一样的,将Vb送到AD7705进行模数转换。然后将其转换成串行序列输出给FPGA处理,同时也上传到DSP控制器。2 软件设计方案本系统的软件设计主要是根据AD7705的特点和操作时序,用FPGA的通用GPIO模拟SPI时序。图4给出了该系统中AD7705的主状态流程图。此后,根据流程图再编写各子模块,即可完成对AD7705两路信号的实时采集。2.1 AD7705的特点及操作时序AD7705是采用∑-△转换技术来实现16位代码无丢失性能的AD

基于FPGA的工控领域监控系统设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com

图3所示为光耦隔离传输电路,由图2所示的差分放大电路输出的电压信号Va经过光耦隔离电路后,即可以l:1的形式传送,即Vb点的电压信号和差分放大后的信号Va是一样的,将Vb送到AD7705进行模数转换。然后将其转换成串行序列输出给FPGA处理,同时也上传到DSP控制器。

2 软件设计方案

本系统的软件设计主要是根据AD7705的特点和操作时序,用FPGA的通用GPIO模拟SPI时序。图4给出了该系统中AD7705的主状态流程图。此后,根据流程图再编写各子模块,即可完成对AD7705两路信号的实时采集。

2.1 AD7705的特点及操作时序

AD7705是采用∑-△转换技术来实现16位代码无丢失性能的AD转换器件。该器件可以直接接收来自传感器的低电平输入信号,然后产生串行的数字输出。AD7705只需2.7~5.25 V的单电源,采用双通道全差分模拟输入,并有一个差分基准输入。当电源电压为5 V、基准电压为2.5 V时,这种器件可对输入信号范围在0~20 mA和0~2.5 V的信号进行处理,还可以处理±20 mV~±2.5 V的双极性输入信号,其串行接口也可配置为三线接口。其增益值、信号极性以及更新速率的选择均可用串行输入口由软件来配置。此外,该器件还包括自校准和系统校准选项,以消除器件本身或系统的增益和偏移误差。

AD7705包括6个用户可通过串口访问的片内寄存器。其中第一个是通讯寄存器,用于管理通道选择,决定下一个操作是读操作还是写操作,以及下一次读或写哪一个寄存器。所有与器件的通讯必须从写通讯寄存器开始。上电或复位后,器件将等待在通讯寄存器上进行一次写操作;

第二个是设置寄存器,用于决定校准模式、增益设置、单/双极性输入以及缓冲模式;

第三个是时钟寄存器,其中包括滤波器选择位和时钟控制位;

第四个是数据寄存器,器件输出的数据从这个寄存器读出;

第五个是零标度校准寄存器,AD7705包含两组独立的零标度寄存器,每个零标度寄存器负责一个输入通道。它们都是24位读,写寄存器;

第六个是满标度校准寄存器,AD7705包含两组独立的满标度寄存器,每个满标度寄存器负责一个输入通道。它们都是24位读/写寄存器。

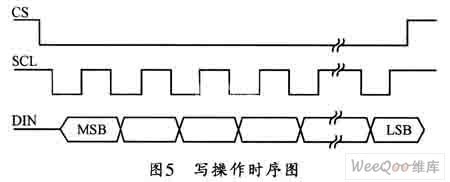

AD7705的写操作时序图如图5所示。在将片选端CS拉低后,即可在串行时钟的上升沿发送数据,发送数据时,高位在前。

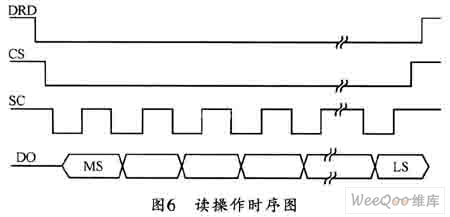

AD7705的读操作时序图如图6所示。当在AD7705的DRDY信号脚检测到逻辑低电平时,表示可以从AD7705的数据寄存器获取新的输出字,当完成对一个完全的输出字的读操作后,DRDY引脚立即回到高电平。如果在两次输出更新之间,不发生数据输出,DRDY将在下一次输出更新前500个输入时钟时间返回高电平。DRDY处于高电平时,不能进行读操作。当数据更新后,DRDY又返回低电平。

《基于FPGA的工控领域监控系统设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的工控领域监控系统设计

- 在谷歌中搜索相关文章:基于FPGA的工控领域监控系统设计

- 在soso中搜索相关文章:基于FPGA的工控领域监控系统设计

- 在搜狗中搜索相关文章:基于FPGA的工控领域监控系统设计

当前位置:

当前位置: