基于FPGA和LVDS技术的光缆传输技术

[09-12 18:30:45] 来源:http://www.88dzw.com EDA/PLD 阅读:8307次

文章摘要:传输模块接收端主要由CLC012均衡器及DS92LV1212解串器组成。DS92LV1212的D00~D09将还原出的并行数据输出,RCLK为还原出的同步时钟,REFCLK为解串器的工作时钟,由FPGA给出。5 软件设计系统上电后,测试台先向采编器发出读数命令,采编器接到命令后,以l Mb/s的速度输出8位并行数据,而LVDS传输器件最低工作速度为16 Mb/s,为了实现速度匹配与自适应,该系统设计采用了Soatan-2E型FPGA内部双口RAM实现FIFO,其时钟最高工作频率为200 MHz,满足要求,当采编器以1 M b/s速度输出数据时,首先进入FPGA内部FIFO,FPGA内部对数据计

基于FPGA和LVDS技术的光缆传输技术,标签:eda技术,eda技术实用教程,http://www.88dzw.com传输模块接收端主要由CLC012均衡器及DS92LV1212解串器组成。DS92LV1212的D00~D09将还原出的并行数据输出,RCLK为还原出的同步时钟,REFCLK为解串器的工作时钟,由FPGA给出。

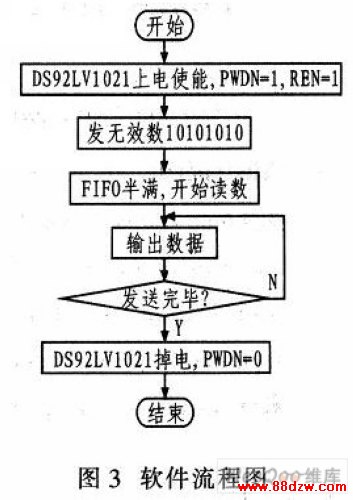

5 软件设计

系统上电后,测试台先向采编器发出读数命令,采编器接到命令后,以l Mb/s的速度输出8位并行数据,而LVDS传输器件最低工作速度为16 Mb/s,为了实现速度匹配与自适应,该系统设计采用了Soatan-2E型FPGA内部双口RAM实现FIFO,其时钟最高工作频率为200 MHz,满足要求,当采编器以1 M b/s速度输出数据时,首先进入FPGA内部FIFO,FPGA内部对数据计数,当存满512个数后,FPGA以20 Mb/s的速度输出8位并行数据,为了保证DS92LVl021一直处于工作状态,FPGA在两次发送数据的间歇所输出的无效数,有效数和无效数通过LVDS传输器件的lO位数据位的高2位数据位作为标志位进行区分,在接收端FPGA通过判断标志位来识别有效数或无效数,舍弃无效数,保证数据正确传输。FPGA在整个系统中起数据缓冲作用,由于采用FIFO作为外部数据接口,所以可实现对外部数据的自适应要求。整个程序用VHDL语言编写,流程图如图3所示。

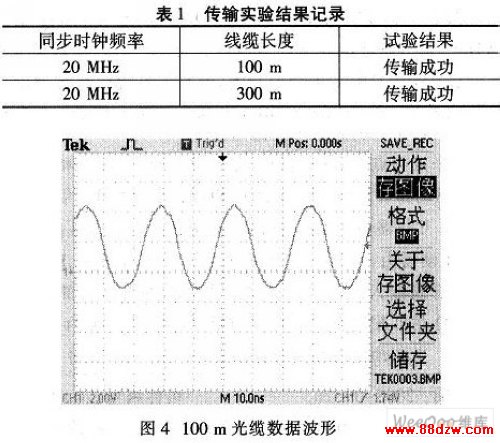

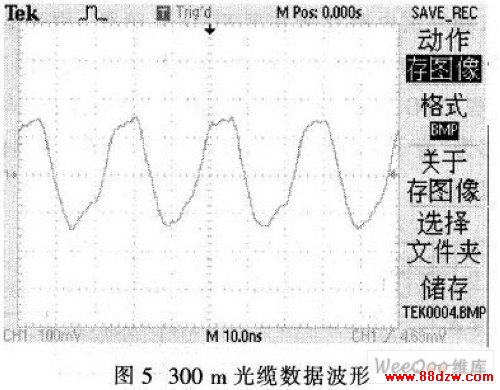

6 试验结果

为了测试最终效果,在发送电路和接收电路之间用不同长度的单模光纤连接,系统上电后,发送端发送数据速度为20 Mb/s,使用示波器捕获接收端数据波形,并进行对比,实验结果记录如表1所列。图4和图5分别给出100 m和300 m光缆的数据波形。由数据波形图知,在传输过程中,波形畸变非常小,没有出现误码和丢数的现象,完全满足系统要求。

7 结语

本文所述LVDS长线传输方案具有电路设计简单,传输速度快,传输距离远的优点,并且对传输速度能够自适应,在需远距离传输的环境中有广阔的应用前景。(国外电子元器件 张时华 任勇峰 李圣昆 刘鑫)

《基于FPGA和LVDS技术的光缆传输技术》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA和LVDS技术的光缆传输技术

- 在谷歌中搜索相关文章:基于FPGA和LVDS技术的光缆传输技术

- 在soso中搜索相关文章:基于FPGA和LVDS技术的光缆传输技术

- 在搜狗中搜索相关文章:基于FPGA和LVDS技术的光缆传输技术

当前位置:

当前位置: