高速FPGA系统的信号完整性测试和分析

[09-12 18:31:18] 来源:http://www.88dzw.com EDA/PLD 阅读:8899次

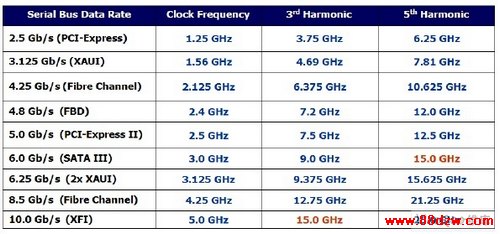

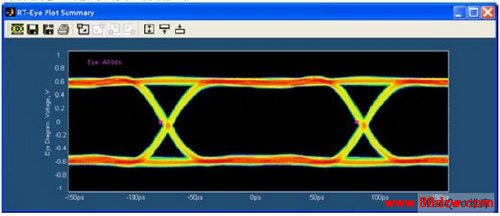

文章摘要:当示波器系统不能提供足够的系统带宽时,它会衰减对高速信号的高次谐波分量。测试结果除了引入由于示波器带宽不足导致的码间干扰(ISI),电压幅度的异常(过冲和衰减),还会导致抖动量过大,最终眼图模板测试的错误或者测试容限的减小,无法真正反映信号完整性问题。图3 分别是泰克TDS6154C 15GHz带宽和传统DSO 13GHz带宽实时示波器对一个FPGA器件提供的的6.25Gb/s高速数据进行的眼图测试结果比较。图中上半部分显示的眼图有很好的对称性,上升和下降时间更快,信号抖动量很小,真实的反映信号的真实特性。由于13GHZ的DSO示波器系统带宽不足,无法捕获信号的五次谐波分量,图中下半部分的测试

高速FPGA系统的信号完整性测试和分析,标签:eda技术,eda技术实用教程,http://www.88dzw.com

当示波器系统不能提供足够的系统带宽时,它会衰减对高速信号的高次谐波分量。测试结果除了引入由于示波器带宽不足导致的码间干扰(ISI),电压幅度的异常(过冲和衰减),还会导致抖动量过大,最终眼图模板测试的错误或者测试容限的减小,无法真正反映信号完整性问题。图3 分别是泰克TDS6154C 15GHz带宽和传统DSO 13GHz带宽实时示波器对一个FPGA器件提供的的6.25Gb/s高速数据进行的眼图测试结果比较。图中上半部分显示的眼图有很好的对称性,上升和下降时间更快,信号抖动量很小,真实的反映信号的真实特性。

由于13GHZ的DSO示波器系统带宽不足,无法捕获信号的五次谐波分量,图中下半部分的测试结果反映出眼图上升时间过慢;同时测试的眼图还存在明显的过冲和震铃,测试仪器导致的抖动也掩盖的信号的真正抖动大小。

图3 高速串行数据测试比较(上图为泰克TDS6154C示波器测试结果)

3.2 示波器高速采集内存的要求

当使用实时示波器对于FPGA信号进行信号完整性测试时,利用一次采集的数据构建眼图,所以除了示波器硬件带宽和高速采样率外,采集的数据量的大小非常关键,这样对示波器的高速采集内存就有了更高的要求。下图是在高采样率下,不同高速内存容量下一次捕获的数据量的大小。

当对FPGA的高速信号进行抖动测试时,高速内存长度不仅决定了一次抖动测试中样本数的多少,还决定了示波器能够测试的抖动频率范围。针对信号中的各种低频抖动干扰源,高速采集内存长度是示波器进行低频抖动测试的关键。下表显示的为20GSa/s高采样率下,不同内存长度分析抖动频率范围的大小。

传统高性能示波器设计构架采用将高速采集前端(多达80颗ADC)和高速内存在物理上用一颗SOC芯片实现,由于有太多功能在一个芯片内部实现,导致片内高速内存容量的限制(在20GS/s下小于1M),无论是对于高速串行数据的眼图测试还是对于时钟信号的抖动测试,都存在很大的限制,并且日后无法对内存扩展升级。

为了弥补这种设计结构的缺陷,这类示波器会采用在芯片外部添加低速存储器弥补片内高速内存的限制,但外部存储器不能在高采样率下工作,一般只能提供2GS/s,样点间隔500ps,由于绝大多数信号边沿速度都在皮秒级,2GS/s无法在信号边沿采集足够样点,甚至出现会出现混叠,所以它无法提供有意义的眼图和抖动测试结果。

泰克TDS6154C高速实时示波器采用硅锗(SiGe)半导体集成采集前端,并使用独立的高速存储器,这样就不受内存长度的限制,并且它同时支持最大采样率和存储长度。

4. 抖动、噪声和BER测试和分析

针对FPGA中不断增长的串行数据传输速率,设计人员不仅进行眼图测试,还需要一套先进的测试和分析工具帮助他们更好地理解和改善他们设计方案的信号完整性。

针对FPGA提供的各种高速串行信号,传统的采样示波器配合抖动分析软件针对FPGA中的高速串行信号能够进行抖动的测试,测试结果的分离,后期的抖动原因的定位和分析,以及水平时间分量上的BER分析。但是,对于导致BER的另一个主要原因,即串行信号中的噪声分量,没有一个彻底的测试和分析方法。图4显示了对于一个高速串行信号的抖动分量和噪声分量影响BER的过程。

《高速FPGA系统的信号完整性测试和分析》相关文章

- › 利用高速FPGA设计PCB的要点及相关指导原则

- › 高速FPGA系统的信号完整性测试和分析

- › 选择最佳的高速FPGA收发器解决方案(推荐)

- 在百度中搜索相关文章:高速FPGA系统的信号完整性测试和分析

- 在谷歌中搜索相关文章:高速FPGA系统的信号完整性测试和分析

- 在soso中搜索相关文章:高速FPGA系统的信号完整性测试和分析

- 在搜狗中搜索相关文章:高速FPGA系统的信号完整性测试和分析

当前位置:

当前位置: