Virtex一5LXl10的ASlC原型开发平台设计

[09-12 18:31:20] 来源:http://www.88dzw.com EDA/PLD 阅读:8532次

文章摘要:接下来为FPGA创建结构化的原理图符号。由于FPGA本身I/0的复杂性和可配置性,将整个FPGA分割为多个子模块能够有效地减轻设计的复杂度,也便于管理和检查。图2显示了利用Mentor Dxdesigner’原理图符号生成向导生成模块化原理图符号的设计过程。原理图符号生成之后就可以在原理图设计环境进行原理图的设计,指定各个模块的连接关系。1.3 PCB叠层定义对。PCB叠层、材料和尺寸的设计需要考虑以下因素:◆走线层的数量需要考虑到封装特性、设计所用的I/()数目以及间距;◆芯片互联线的数据传输速率,信号的上升、下降时间对PCB材料、尺寸以及走线方式和制板工艺的限制;◆元件所需的不同供电和参考

Virtex一5LXl10的ASlC原型开发平台设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com

接下来为FPGA创建结构化的原理图符号。由于FPGA本身I/0的复杂性和可配置性,将整个FPGA分割为多个子模块能够有效地减轻设计的复杂度,也便于管理和检查。图2显示了利用Mentor Dxdesigner’原理图符号生成向导生成模块化原理图符号的设计过程。原理图符号生成之后就可以在原理图设计环境进行原理图的设计,指定各个模块的连接关系。

1.3 PCB叠层定义

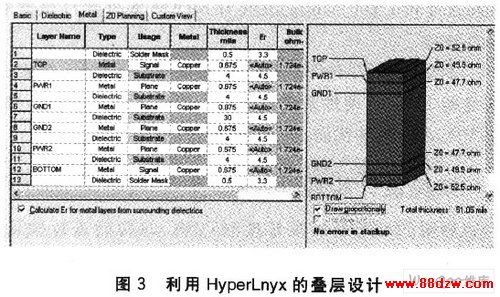

对。PCB叠层、材料和尺寸的设计需要考虑以下因素:

◆走线层的数量需要考虑到封装特性、设计所用的I/()数目以及间距;

◆芯片互联线的数据传输速率,信号的上升、下降时间对PCB材料、尺寸以及走线方式和制板工艺的限制;

◆元件所需的不同供电和参考电压,对电源层的规划和设计;

◆成本问题(利用盲孔、盲埋孔、微通孔等工艺能有效地减少叠层数目,以达到降低成本的目的)。

该设计中,与FPGA互联的信号线约为130条,包括配置电路信号线、时钟信号线及其他I/O信号。选用上下两个走线层。考虑到多个电源供电,设置2个电源平面、2个地平面。整个PCB采用6层板结构设计,信号层目标阻抗50 Q。

利用HyperLnyx叠层设计如图3所示。

1.4 散热管理

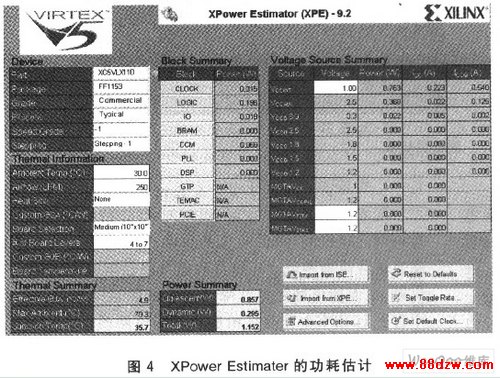

FPGA支持的速率越高,本身的资源密度越大,因此要关注应用中的散热管理问题。对FPGA的功率消耗进行估计,以决定是否需要散热系统。

XPower Estimater是一款基于Excel的软件,通过对设计资源的利用,包括逻辑资源、DCM、PLL、I/0类型、触发率(toggling rate),以及其他与FPGA设计密切相关的信息,对FPGA的功耗进行估算。图4为利用XPE进行设计功耗估算的截图。

1.5 信号完整性分析

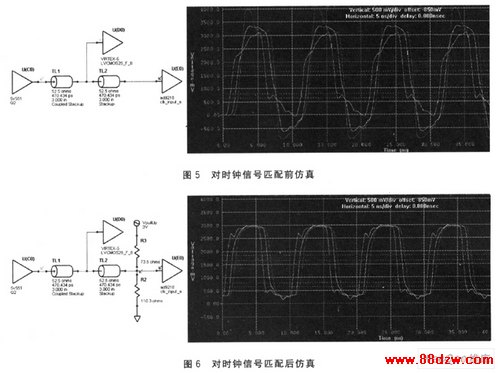

在时域和频域对设计的连接拓扑结构(PCB叠层、驱动端、接收端、连接器、通孔等等)进行信号完整性分析,目的是要*估和减小信号从驱动端到接收端的反射、串扰以及EMI/EMC等问题。通过仿真分析得到的约束形式能有效指导PCB布局布线工具进行layout设计。进行信号完整性分析,首先要确定与FPGA相接的外围器件的I/O特性及其约束,进而对FPGA采用何种I/0类型以及端接匹配机制有一个大致的了解,然后是通过仿真对采用的I/O类型及端接电路的各个参数进行定义及优化。

(1)前仿真

S1分析一般主要从高速信号、对时序要求较高的信号、走线最长的信号、负载最多的信号开始,因为这些信号线通常最容易引起SI问题。确定关键信号在仿真环境中建立起相应的拓扑模型。

通过仿真能定义出最长连接走线以及其他满足噪声裕量(匹配电路、端接方式等)的网络属性。确定FPGA驱动缓冲特性,例如I/O标准、驱动能力以及回转率,使信号完整性问题、EMI/EMC问题最小化,同样也对接收端I/0属性进行定义。进行串扰仿真以保证相邻走线不会引起串扰问题。定义端节匹配方式。

图5、6是对时钟网络匹配前和匹配后进行的仿真图形对比。

通过前期的大量仿真分析可以很好地保证设计的成功率。

(2)后仿真

《Virtex一5LXl10的ASlC原型开发平台设计》相关文章

- › 基于Virtools 和串口通信的界面交互性的设计与实现

- › Virtex一5LXl10的ASlC原型开发平台设计

- › 安富利发布Xilinx Virtex-6 FPGA DSP开发工具套件

- › 赛灵思高性能40nm Virtex-6 FPGA系列通过验证

- 在百度中搜索相关文章:Virtex一5LXl10的ASlC原型开发平台设计

- 在谷歌中搜索相关文章:Virtex一5LXl10的ASlC原型开发平台设计

- 在soso中搜索相关文章:Virtex一5LXl10的ASlC原型开发平台设计

- 在搜狗中搜索相关文章:Virtex一5LXl10的ASlC原型开发平台设计

当前位置:

当前位置: