如何提高基于FPGA的原型的可视性

[09-12 18:31:32] 来源:http://www.88dzw.com EDA/PLD 阅读:8779次

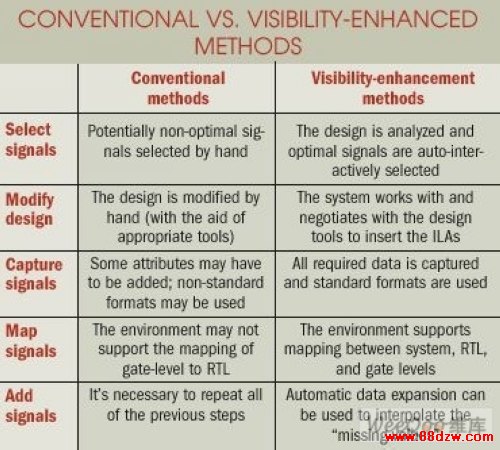

文章摘要:特别地,这种数据扩展可以填充位于信号被捕获的寄存器之间的组合逻辑区块内部的信号。为了最大限度地提高性能,只对进行试验的逻辑进行动态的数据扩展,而不是对所有设计逻辑进行静态的数据扩展。传统设计环境与其可视性增强环境的对比如表所示。可视性增强技术可以极大地加快定位、隔离和了解基于FPGA的原型中的错误症状原因的过程(类似的技术可以应用于基于FPGA的仿真和软件仿真中)。在一般的设计中,寄存器约占信号的20%。采用可视性增强技术允许设计工程师将这些信号作为确定余下80%信号的值的基础,这相当于可视性提高了大约五倍。而据使用这种技术的用户报告,调试时间减少了四倍。换言之,在不使用可视性增强技术的情况下

如何提高基于FPGA的原型的可视性,标签:eda技术,eda技术实用教程,http://www.88dzw.com特别地,这种数据扩展可以填充位于信号被捕获的寄存器之间的组合逻辑区块内部的信号。为了最大限度地提高性能,只对进行试验的逻辑进行动态的数据扩展,而不是对所有设计逻辑进行静态的数据扩展。传统设计环境与其可视性增强环境的对比如表所示。

可视性增强技术可以极大地加快定位、隔离和了解基于FPGA的原型中的错误症状原因的过程(类似的技术可以应用于基于FPGA的仿真和软件仿真中)。

在一般的设计中,寄存器约占信号的20%。采用可视性增强技术允许设计工程师将这些信号作为确定余下80%信号的值的基础,这相当于可视性提高了大约五倍。而据使用这种技术的用户报告,调试时间减少了四倍。换言之,在不使用可视性增强技术的情况下调试所用的每一个小时在使用该技术之后都可以缩短至仅15分钟。

就未来而言,可视性增强环境提供的数据扩展能力为将内部FPGA信号数据与一般只在软件仿真环境下考虑的先进调试技术搭配使用提供了基础。例如,如果设备包含复杂的内部总线,扩展的数据可能会在事务级被查看,从而使了解设备的操作更加容易。在调试器环境中谨慎地集成数据扩展技术可以同时缩短验证运行时间和最终的捕获数据文件大小。这种环境将实现自动化向导调试以及先进的分析和跟踪能力。

本文小结

使用基于FPGA的原型的设计和验证团队所面临的最大挑战之一是当系统未能按期望执行时了解系统的内部行为。可视性增强验证和调试环境通过以下方式解决了这个问题:帮助选择要观察的信号;与其它工具配合工作(和协商),从而对设计进行修改以捕获所选的信号;捕获所有驱动下游工具必需的数据和属性;使用先进的技术在系统、RTL和门级视图之间自动映射;执行数据扩展以填充未被捕获的信号的值。

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《如何提高基于FPGA的原型的可视性》相关文章

- › 如何提高摩托车发动机动力性能

- › 如何提高LED显示屏远距离通讯的稳定性

- › 如何提高基于FPGA的原型的可视性

- › 如何提高PCB的焊接质量

- › 如何提高PCB阻焊剂的外观质量

- 在百度中搜索相关文章:如何提高基于FPGA的原型的可视性

- 在谷歌中搜索相关文章:如何提高基于FPGA的原型的可视性

- 在soso中搜索相关文章:如何提高基于FPGA的原型的可视性

- 在搜狗中搜索相关文章:如何提高基于FPGA的原型的可视性

分类导航

最新更新

当前位置:

当前位置: