基于CPLD的CCD信号发生器的研究

[09-12 18:31:55] 来源:http://www.88dzw.com EDA/PLD 阅读:8773次

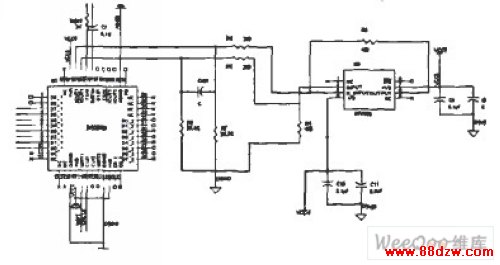

文章摘要:图5数模转换模块的DXP原理图6 提高信号精度经过上述的数字的信号生成,数模转换及转换,基本上可以得到所需要的频率为11 MHz 的信号波形。信号上叠加了很多的高频噪声,无法满足下级采样系统对低噪声的要求。因此 需要从PCB的布局、布线及器件的配置等多个角度人手,对信号进行改进,把噪声限制在10 mV 以下,主要从以下三方面来提升系统性能,抑制噪声:(1)电源滤波部分。电源噪声的危害最大,通过对电源部分增加滤波电路来滤除电源 噪声,同时因为大旁路电容可能因谐振而失效,所以在电路板上布置了一些比较小的旁路电 容阵列,CPLD器件的每个供电电压管脚都要外接0.1μ ,电容来进行滤波。(2)由于系统

基于CPLD的CCD信号发生器的研究,标签:eda技术,eda技术实用教程,http://www.88dzw.com

图5数模转换模块的DXP原理图

6 提高信号精度

经过上述的数字的信号生成,数模转换及转换,基本上可以得到所需要的频率为11 MHz 的信号波形。信号上叠加了很多的高频噪声,无法满足下级采样系统对低噪声的要求。因此 需要从PCB的布局、布线及器件的配置等多个角度人手,对信号进行改进,把噪声限制在10 mV 以下,主要从以下三方面来提升系统性能,抑制噪声:

(1)电源滤波部分。电源噪声的危害最大,通过对电源部分增加滤波电路来滤除电源 噪声,同时因为大旁路电容可能因谐振而失效,所以在电路板上布置了一些比较小的旁路电 容阵列,CPLD器件的每个供电电压管脚都要外接0.1μ ,电容来进行滤波。

(2)由于系统工作在较高的频率,所以要考虑到信号的完整性问题,即解决信号的反 射及信号之间的串扰问题。选取串联端接的方法,并且将匹配电阻尽量靠近信号发送端。同 时将设计完成的PCB图导入CADENCE软件进行仿真,确定最佳的串联电阻值,实际系统通过串 联匹配电阻后,信号的过冲和振铃现象得到了有效的消除。

(3)增加模拟一阶有源滤波电路。通过示波器发现生成信号上叠加有高频噪声,为了 滤除该噪声,选用OPA680放大器构成有源低通滤波电路。通过调节器件参数来改变滤波器的 低通频率范围,大大方便了系统调试,有效的滤除了高频噪声。在接插件管脚增加RC低通滤 波电路,实际证明对提高信号质量有一定的改善作用。

7 结束语

编译仿真通过后,在顶层用原理图进行综合实现,然后烧入芯片进行实验,并根据实际 运行情况,对设计进行改进。如根据实际器件的延时特性.在设计中某些地方插入适当的延 迟单元以保证各时延一致。本设计完成了CCD 输出信号仿真,并给出最终仿真波形。我们对 设计的信号发生器在不同配置数据下的输出信号进行了测试,信号的波形和信噪比都完全能 达到系统所要求的性能指标,从而表明该设计方案是行之有效的。

本文作者创新点:本文设计了一种基于CPLD的可编程高精度CCD信号发生器。充分利用CPLD的可编程性.模拟出满足系统要求的CD信号,输出信号频率达到1IMHZ。

《基于CPLD的CCD信号发生器的研究》相关文章

- › 基于CPCI总线的多网口卡设计

- › 一种基于CPLD的声发射信号传输系统设计

- › 基于CPLD的臭氧电源控制系统的软硬件设计

- › 基于CPLD/FPGA的CMI编码设计与实现

- › 基于CPLD的压电生物传感器检测电路设计

- › 基于CPLD的CCD信号发生器的研究

- 在百度中搜索相关文章:基于CPLD的CCD信号发生器的研究

- 在谷歌中搜索相关文章:基于CPLD的CCD信号发生器的研究

- 在soso中搜索相关文章:基于CPLD的CCD信号发生器的研究

- 在搜狗中搜索相关文章:基于CPLD的CCD信号发生器的研究

当前位置:

当前位置: