可实现快速锁定的FPGA片内延时锁相环设计

[09-12 18:32:02] 来源:http://www.88dzw.com EDA/PLD 阅读:8446次

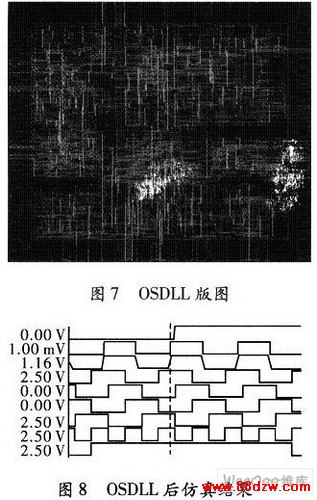

文章摘要:基于SMIC O.25 μm工艺,设计OSDLL测试芯片。OSDLL的工作频率在20~200 MHz之间,工作电压为2.5 V。图7为版图,图8为版图后仿真结果。3 结束语介绍了DLL架构和工作原理,并基于原DLL结构,加入快速锁定one-shot模块。新的DLL结构OSDLL在提高DLL锁定速度的基础上,没有过多的增加硬件资源,保持了原DLL的时钟综合能力和抗抖动功能。在SMIC 0.25μm工艺下,设计完成OSDLL测试芯片,其工作频率在20~200 MHz之间,锁定时间比传统架构大幅降低。OSDLL架构集成于FPGA芯片内,可有效地优化设计时序,加强系统性能。(电子科技 合肥工业大学 王

可实现快速锁定的FPGA片内延时锁相环设计,标签:eda技术,eda技术实用教程,http://www.88dzw.com 基于SMIC O.25 μm工艺,设计OSDLL测试芯片。OSDLL的工作频率在20~200 MHz之间,工作电压为2.5 V。图7为版图,图8为版图后仿真结果。

3 结束语

介绍了DLL架构和工作原理,并基于原DLL结构,加入快速锁定one-shot模块。新的DLL结构OSDLL在提高DLL锁定速度的基础上,没有过多的增加硬件资源,保持了原DLL的时钟综合能力和抗抖动功能。在SMIC 0.25μm工艺下,设计完成OSDLL测试芯片,其工作频率在20~200 MHz之间,锁定时间比传统架构大幅降低。OSDLL架构集成于FPGA芯片内,可有效地优化设计时序,加强系统性能。(电子科技 合肥工业大学 王忠涛 杨明武)

Tag:EDA/PLD,eda技术,eda技术实用教程,EDA/PLD

《可实现快速锁定的FPGA片内延时锁相环设计》相关文章

- › 可实现快速锁定的FPGA片内延时锁相环设计

- 在百度中搜索相关文章:可实现快速锁定的FPGA片内延时锁相环设计

- 在谷歌中搜索相关文章:可实现快速锁定的FPGA片内延时锁相环设计

- 在soso中搜索相关文章:可实现快速锁定的FPGA片内延时锁相环设计

- 在搜狗中搜索相关文章:可实现快速锁定的FPGA片内延时锁相环设计

分类导航

最新更新

当前位置:

当前位置: