基于FPGA的任意波形发生器设计与实现

[09-12 18:32:10] 来源:http://www.88dzw.com EDA/PLD 阅读:8713次

文章摘要:摘要:本文提出了一种基于可编程逻辑器件(FPGA)芯片EP2C20F484的任意波形发生器的设计方法。完成了在FPGA的控制下,USB接口控制模块、SRAM控制模块、DA转换模块等协同工作的硬件设计、固件设计以及软件设计,并给出了实验结果。实验结果表明,此任意波形发生器能够按照要求输出相应波形,达到了设计要求。0 引言在腐蚀领域和电镀行业,常常需要使用任意波形的电流电压信号进行生产和测试。任意波形是指频率可变、幅值可变、相位可变的正弦波形和其他波形,如三角波形、锯齿波、特殊波形等。目前任意波形发生器大多采用直接数字频率合成(DDS)技术,即将波形的数字量信号存储于存储器中,嵌入式主机以一定的速

基于FPGA的任意波形发生器设计与实现,标签:eda技术,eda技术实用教程,http://www.88dzw.com摘要:本文提出了一种基于可编程逻辑器件(FPGA)芯片EP2C20F484的任意波形发生器的设计方法。完成了在FPGA的控制下,USB接口控制模块、SRAM控制模块、DA转换模块等协同工作的硬件设计、固件设计以及软件设计,并给出了实验结果。实验结果表明,此任意波形发生器能够按照要求输出相应波形,达到了设计要求。

0 引言

在腐蚀领域和电镀行业,常常需要使用任意波形的电流电压信号进行生产和测试。任意波形是指频率可变、幅值可变、相位可变的正弦波形和其他波形,如三角波形、锯齿波、特殊波形等。目前任意波形发生器大多采用直接数字频率合成(DDS)技术,即将波形的数字量信号存储于存储器中,嵌入式主机以一定的速率依次将存储器单元中的波形数据逐个发送给D/A转换器,合成为需要的波形。

随着微处理器日益广泛的应用和大规模集成电路技术的发展,出现了大量能够产生多种波形且性能稳定的任意波形发生器,但大多数方案都是基于串行或并行总线进行数据的传输,这种方案虽然成本较低,但系统的实时性较差,难以满足复杂波形的大数据量的传输要求。我们设计了一种基于FPGA芯片的任意波形发生器,充分利用了FPGA强大的逻辑功能,实现了利用单片FPGA芯片控制整个系统的方案。同时选择USB2.0接口芯片CY7C68013,它能较好地与FPGA芯片合作,完成系统预先设计的功能,使总体电路简单,成本低廉,产生的波形信号精度较高。数字波形数据从上位机通过USB总线直接存储在SRAM数据存储器中,通过FPGA控制,将波形数据读出,送入后向通道进行D/A转换和放大处理后得到所需的模拟信号波形。与传统的发生器在ROM或FLASH存储波形数据的方法相比,具有更大的灵活性。

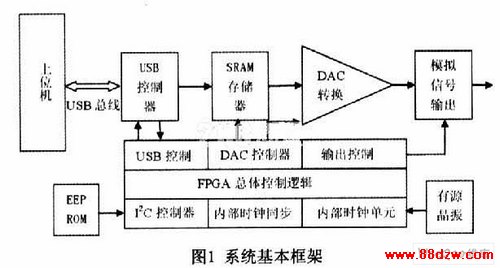

1 系统总体结构及工作过程

波形发生器以FPGA为核心,它控制着整个系统的读、写、输出等操作,系统框图如图l所示。上位机将数字波形数据通过USB2.O总线送到数据存储器中,数据存储器循环地将波形数据发送到DAC电路,由DDS电路产生相应的DAC刷新时钟(0~1MHz,步进0.02Hz),DAC输出波形经缓冲放大、低通滤波、放大输出。输出的波形频率为0.1Hz(DC)~1MHz(-3dB),频率分辨率为0.01Hz。

本系统主要由五部分组成:

(1)上位机。主要功能是利用仿真软件(如CVI、MATLAB、VB等)产生所需波形数据,并通过USB接口下载到波形发生器中,其次就是存储USB2.0接口芯片的驱动程序。

(2)USB2.0接口控制器芯片。本设计使用的是Cvpress Semiconductor公司的EZ-USB FX2系列芯片CY7C68013AE。

(3)数据存储芯片SRAM。考虑到成本的因素,本系统采用ISSI公司的IS6lLV25616-10T。

(4)D/A转换芯片。本设计使用的是AD9726,该芯片控制信号简单,D/A转换速度快,因此将系统的硬件设计大为简化,也减轻了系统软件设计的工作量。

(5)FPGA控制芯片。本设计使用的是Altera公司的Cyclone II系列型号为EP2C20F484的FPGA。EP2C20F484以90nm工艺技术为基础,提供了18,752个逻辑单元(LE),并具有一整套最佳的功能,包括嵌入式18位×18位乘法器、专用外部存储器接口电路、4kbit嵌入式存储器块、锁相环(PLL)和高速差分I/O能力等。

2 系统功能及硬件实现

2.1 USB传输模块

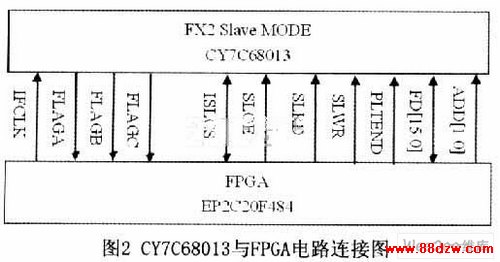

CY7C68013有2种接口方式:Slave FIFOs和可编程接口GPIF。当FPGA与其相连时,只需要利用CY7C68013作为一个USB2.0数据通道来实现与主机的高速通信。

Slave FIFOs方式是从机方式,外部控制器可像普通FIFO一样对CY7C68013的多层缓冲FIFO进行读写。CY7C68013的Slave FIFOs工作方式可设为同步或异步;工作时钟可选为内部产生或外部输入,其它控制信号也可灵活地设置为高有效或低有效。电路连接图如图2所示。

《基于FPGA的任意波形发生器设计与实现》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的任意波形发生器设计与实现

- 在谷歌中搜索相关文章:基于FPGA的任意波形发生器设计与实现

- 在soso中搜索相关文章:基于FPGA的任意波形发生器设计与实现

- 在搜狗中搜索相关文章:基于FPGA的任意波形发生器设计与实现

当前位置:

当前位置: